G-NAVPTM 架構電路的設計方法與佈局注意事項

摘要

在設計程序中,元件值的設計和 PCB 佈局對電源的性能有很大的影響。若能注意 PCB 佈局上的細節,對於能有低開關損耗、乾淨無雜訊及穩定的操作是非常重要的。適當的選擇元件可以使所設計的電源較容易通過英特爾 (Intel) 及 AMD 的規格。此應用須知將介紹 G-NAVPTM 控制架構電路的設計方法,包括:導通時間設定、開關頻率設定、負載線設定和 DCR 電流檢測網路設定。最後,將對 PCB 的佈局規則提出建議,以期降低雜訊干擾,使控制器更為可靠。

1.

設計方法與元件選擇

以下的設計方法是以 RT8884B 為例子,並滿足英特爾的 VR12.5 規格。在應用 RT8884B 時,有三個主要的設計步驟:第一步是導通時間和開關頻率的初始設定,第二步是 DCR 電流檢測網路的設計,而最後一步則是完成負載線的設計。

|

CPU操作條件

|

|

輸入電壓

|

12V

|

|

相位數

|

3

|

|

VBOOT

|

1.7V

|

|

VDAC(MAX)

|

1.85V

|

|

ICCMAX

|

106A

|

|

ICC-DY

|

60A

|

|

ICC-TDC

|

55A

|

|

負載線

|

1.5mΩ

|

|

快速電壓迴轉率

|

12.5mΩ/µs

|

|

最大開關頻率

|

300kHz

|

請參閱 Shark Bay VRTB 電力輸送指南,其中所建議的輸出濾波器如下所示:

輸出電感:360nH / 0.72mΩ

輸出大型電容:560µF / 2.5V / 5mΩ (max),4 至 5 個

輸出陶瓷電容:22µF / 0805 (在上層最多可放 18 個)

1.1.

導通時間與開關頻率的初始設定

一般說來,較高的開關頻率可產生較快的瞬態響應和較小的穩態輸出漣波,並且可使用較小尺寸的功率元件和印刷電路板的空間。然而,較高的開關頻率通常導致較低的轉換效率,較差的抗雜訊能力及有過熱的問題;因此,最大開關頻率的合理範圍是受到以上綜合因素的限制。最大開關頻率一旦決定了之後,用開關頻率和責任週期之間的關係即可算出最大導通時間。

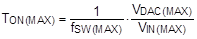

(1)

(1)

其中,VDAC(MAX) 是參考電壓,fSW(MAX) 是最大開關頻率,而 VIN(MAX) 是最大輸入電壓。下面所顯示是以設計 RT8884B 為例。

因為 RT8884B 採用固定導通時間控制, CCRCOT(固定電流漣波之 COT)此項專利技術是利用輸入電壓和 VID 碼來產生適應性的導通時間,及固定的電流漣波;如此可在不同的輸入和輸出電壓範圍內,將輸出電壓漣波控制到幾乎是固定的。在輸入電壓端子和 TONSET 接腳之間接上的電阻 RTON ,可用來設定導通時間。

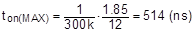

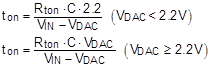

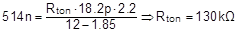

(2)

(2)

其中 C = 18.2pF,VIN 是最大輸入電壓,VDAC 是參考電壓,而 TON 是方程式 (1) 所決定的導通時間。下面所計算的也是以 RT8884B 為例。

1.2.

DCR 電流檢測網路之設計

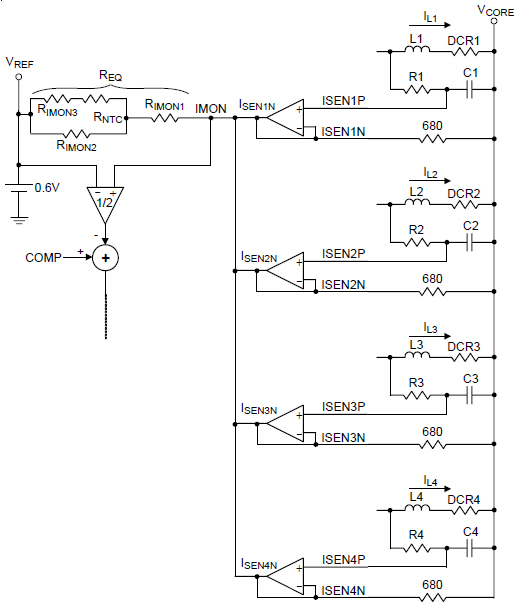

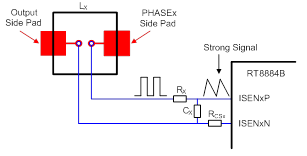

圖一、RT8884B 完整電流迴路示意圖。

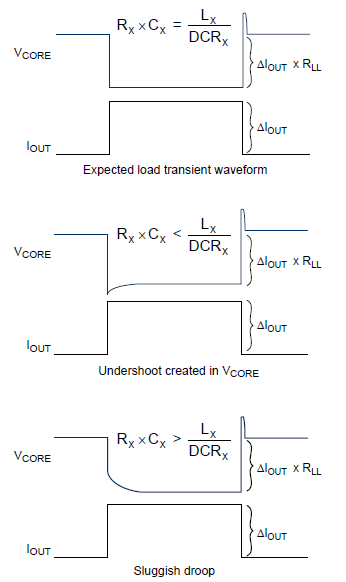

圖二、對應不同 τCx 和 τLx 時間常數關係的輸出波形。

圖一顯示應用 RT8884B 時,完整的電流迴路圖。在ACLL性能和DCLL精確度上,DCR電流檢測的電路設計扮演非常重要的角色。對於不同 RC 時間常數的設計,ACLL 輸出電壓的瞬態變化可分成以下三種情況。圖二即顯示了對應三種不同 τCx 和 τLx 時間常數關係的輸出波形。

• 若 τCx 等於 τLx,預期的負載瞬態波形是可設計的。

• 若 τCx 小於 τLx,輸出電壓會突然下降,下衝規格的裕量會減少。

• 若 τCx 大於 τLx,在負載增加時,輸出電壓會緩慢地下降。

(3)

(3)

其中,DCRx 是電感的等效電阻、Lx 是電感值,而 Rx 和 Cx 是 DCR 電流檢測網路中的元件值。

通常會將時間常數 τCx 設計為等於或稍大於時間常數 τLx,以防止過衝和下衝,如此電路便有較多的裕量可通過設計的規格。特別要注意的是,Cx值可能會因為偏壓,溫度或頻率...等因素變小,所以在設計 DCR 電流檢測網路時,需要將Cx 值變小的效應考慮進來。

由於電感器的銅線具有正溫度係數,DCR 值會隨負載電流的增加而線性增加。因此,為了達到更好的 DCLL 性能,必須使用由 NTC 熱敏電阻(REQ)構成的熱補償電路,以補償電感 DCR的正溫度係數。詳細的熱補償電路設計,可以參考特定產品的設計工具。

1.3.

負載線設計

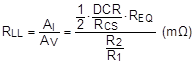

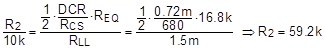

在 G-NAVPTM 架構中,負載線的設計和電流迴路增益與電壓迴路增益之比有關。詳細的負載線方程式均可在對應的 IC 規格書中找到。以下以 RT8884B 為例。

(4)

(4)

其中,DCR(25℃)= 0.72mΩ,RCS = 680Ω 是電流檢測電阻,REQ(25℃)是用於熱補償設計的電阻值,而 R2 / R1是補償器的AV 增益。藉由此方程式,可以透過調整補償器的 AV 增益而很容易地改變負載線。按照英特爾的VR12.5 的要求,負載線須是1.5(mΩ),所以就可以算出了 AV 增益 R2 / R1。 以下以 RT8884B 作為範例,並且選 R1=10KΩ。

2. 佈局注意事項

若能注意印刷電路板上佈局的細節,對於能有低開關損耗、乾淨無雜訊及穩定的操作是非常重要的。開關功率級則特別需要留意。如果可能的話,應將所有功率元件放在電路板的上方,並且使接地端子相互靠近。參考以下佈局原則,有助於能有最佳性能的 PCB 佈局:

2.1.

功率級佈局原則

• 盡量保持大電流的路徑短愈短愈好,特別是接地端子的。

• 盡可能保持電源走線和負載之間的連線都很短;這對達到高效率是非常重要的。

• 若必須在電感的充電路徑和放電路徑之間作取捨,較好的選擇是讓電感的充電路徑比放電路徑長。

2.2.

IC檢測墊和RGND佈局原則

• 盡量將電流檢測元件(CX, RCSX, RX)放置靠近控制器的位置,以避免電流檢測信號被雜訊干擾。

圖三、電流檢測元件的放置。

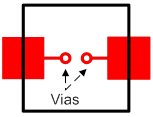

• 作為電流限制和電壓定位的 ISENxP 和 ISENxN,其連線方式必須採用凱文 (Kelvin) 檢測連接法,以確保電流檢測的精確度。電感的走線是直接從電感的接觸墊開始,而不是從電感的連接平面。

圖四、電流檢測走線中的電感接觸墊。

• 從電感檢測節點出來的 PCB 走線都應平行地回控制器。通常,這些走線都走電感下方的 PCB 底層。如果這些走線是走在內層,則必須在電流檢測走線之上有一個接地平面,以作為和上層之間的屏蔽。

• 盡量將高速開關節點 (PWM,UG,LG,相位,等...) 遠離較敏感的類比區域(COMP,FB,ISENxP,ISENxN,等...)。

• 使用者需要透過低阻抗路徑將散熱焊盤連接到接地平面。建議至少使用5個通孔 (via) 連接到 PCB 內層的接地平面。

3. 實驗結果與結論

3.1. 實驗結果

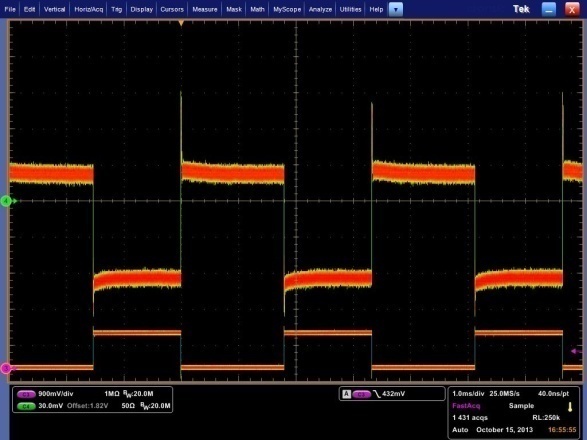

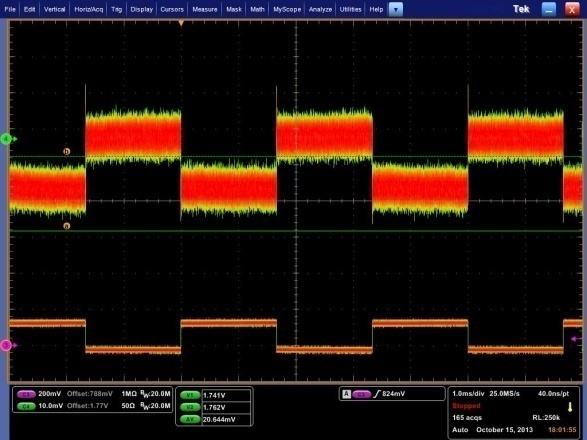

圖五顯示了RT8884B EVB樣品,這是用在 VR12.5 之應用中,並支援 4/3/2/1相。量測的負載線曲線和效率均顯示在圖六。從所測量的結果可知,G-NAVPTM 架構可提供準確的負載線,並仍然維持較高的效率。圖七顯示瞬態的大抽載變化和小抽載變化之波形,由圖可看出快速和穩定的瞬態性能並良好的 AVP 控制。

圖五、RT8884B的 EVB 樣本。

表一、EVB測試條件

|

VIN

|

12V

|

|

VOUT

|

1.8V @PS0

|

|

Phase Number

|

4

|

|

Ls

|

360nH / 0.72mΩ

|

|

Co

|

OSCON : 470µF / 4.5mΩ*4

MLCC : 22µF*19

|

圖六、量測 RT8884B 的負載線和效率。

(CH3: 抽載電流 (900mV/Div) ; CH4: 輸出電壓 (30mV/Div))

(a) 大抽載變化(1A-61A) ACLL @300Hz (b) 小負載變化(50A-60A) ACLL @300Hz

圖七、RT8884B ACLL 之測量結果。

3.2.

結論

系統的元件設計通常需要在許多的限制之間作出取捨,以獲得在效率和性能中最大的效益。此外,有一些特殊的佈局技巧可減少寄生元件的影響,以避免高速開關雜訊耦合的效應。本應用須知介紹了 G-NAVPTM 控制架構一般的設計方法和 PCB 佈局的規則。按照以上所介紹的方式,使用者即可很容易地使用立錡的控制IC。

4. 參考資料

[1] 立錡科技, RT8884B 規格書.

[2] Intel 文件, “Shark Bay Ultrabook™ Platform Power Delivery”

[3] Intel 文件, “Shark Bay Mobile Platform Power Delivery”

[4] Intel 文件, “Shark Bay Desktop and Denlow-WS Platform”