## **RTQ5132**

## **DDR5 Client VR on DIMM PMIC**

### 1 General Description

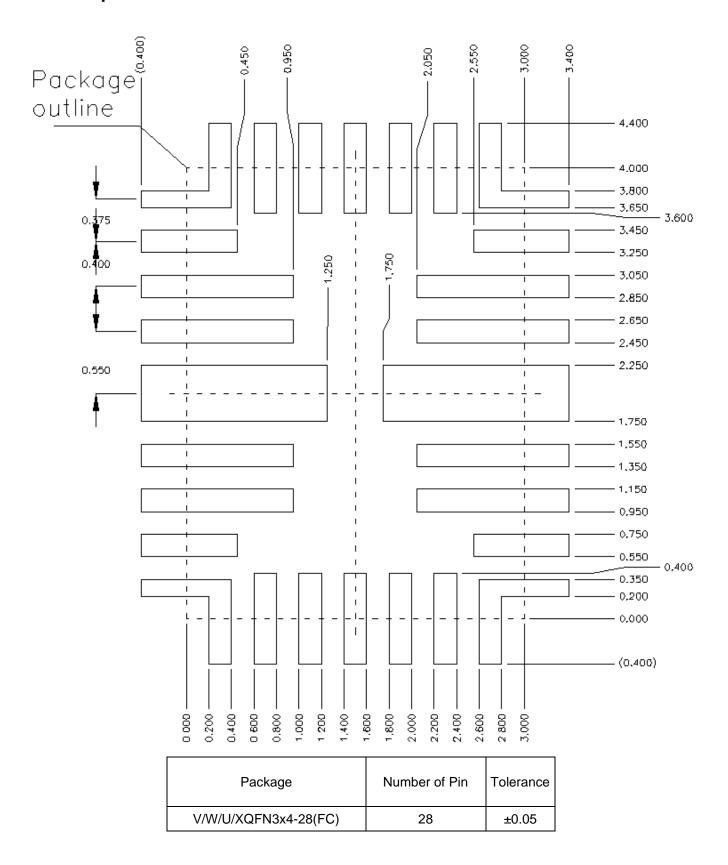

The RTQ5132 is an integrated power management IC designed for general DDR5 SODIMM and UDIMM applications. This device provides three Buck converters (SWA, SWB, and SWC) and two LDOs (VLDO\_1.0V and VLDO\_1.8V). Additionally, the RTQ5132 supports a selectable interface (I<sup>2</sup>C or I3C basic) accommodate various application environments. Α comprehensive protection mechanism is embedded to ensure safe power distribution, with the capability to record fault events in registers and signal them through PWR\_GOOD and GSI\_n open-drain indicators. The RTQ5132 is available in a WQFN-28L 3x4 (FC) package. The recommended junction temperature range is from -10°C to 125°C and the ambient temperature range is from 0°C to 85°C.

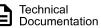

## 2 Ordering Information

#### Note 1.

- Marked with (1) indicated: Compatible with the current requirements of IPC/JEDEC J-STD-020.

- Marked with (2) indicated: Richtek products are Richtek Green Policy compliant.

## 3 Marking Information

marking information, contact our representative directly or through a Richtek distributor located in your area.

### 4 Features

- VIN Bulk with Input Supply Range: 4.25V to 5.5V

- High Integration:

- Three High Efficiency Buck Converters

- SWA: ITDC = 4A. IMAX = 5A

- SWB: ITDC = 4A, IMAX = 5A

- SWC: ITDC = 1A, IMAX = 2A

- Two LDOs

- VLDO\_1.8V: IMAX = 25mA

- VLDO\_1.0V: IMAX = 20mA

- 0.75% Converter Output Accuracy

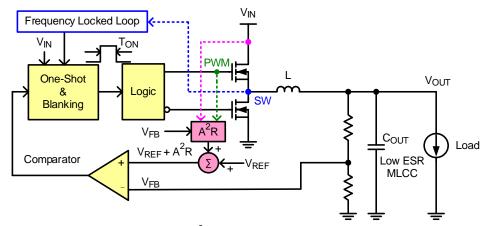

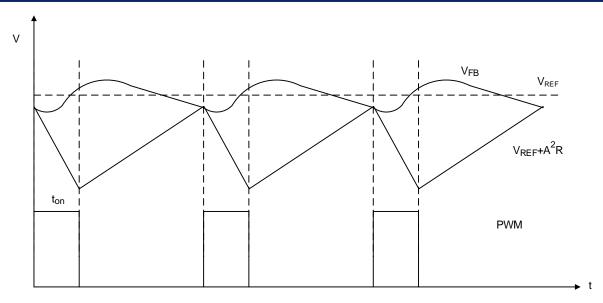

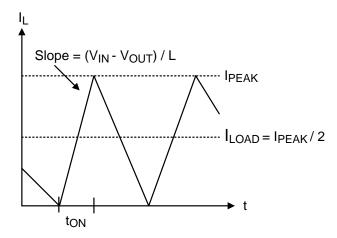

- Fast Transient Response with A<sup>2</sup>RCOT Control

- Support I<sup>2</sup>C and I3C Slave Control

- Error Log Counter and Data Storage (NVM)

- MTP Registers with Secured R/W Access

- Programmable and DIMM Specific Registers for Customization

- Programmable Mode for Debug and Validation

- Telemetry for Output Current, Voltage, and **Power**

- Complete Protection Mechanisms

- VIN\_Bulk Input Supply OVP

- OVP, UVP, OCP, HCW for Each Rails

- High Temp Warning and OTP

- General Status Interrupt Function

- Power-Good Indicator

## 5 Applications

DDR5 SODIMM/ UDIMM

RICHTEK

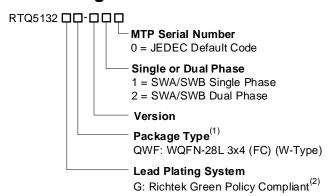

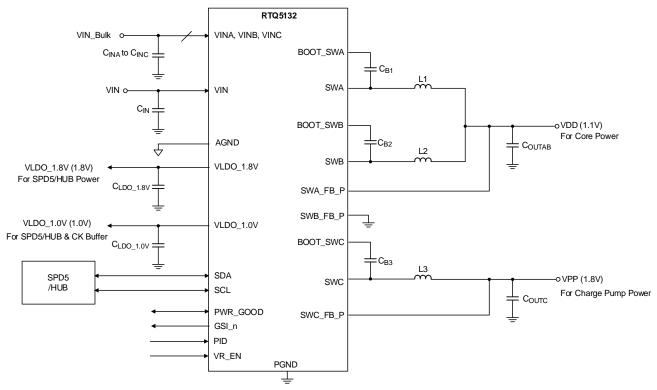

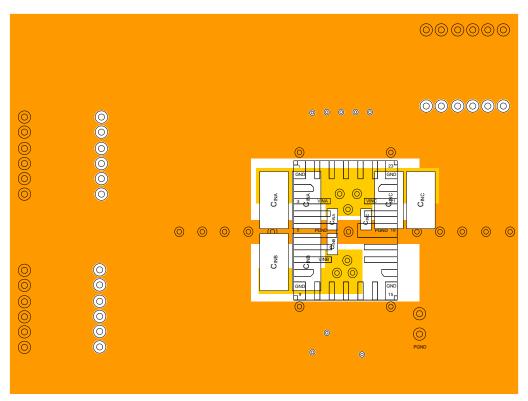

## **6 Simplified Application Circuit**

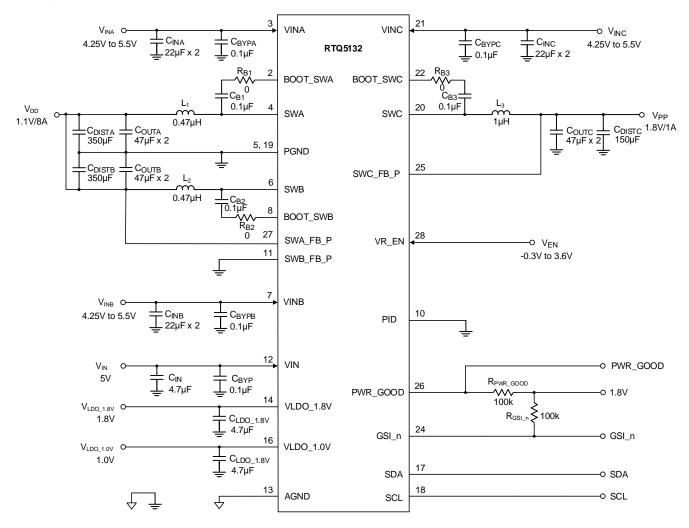

Figure 1. SWA and SWB are combined as Dual-Phase Mode

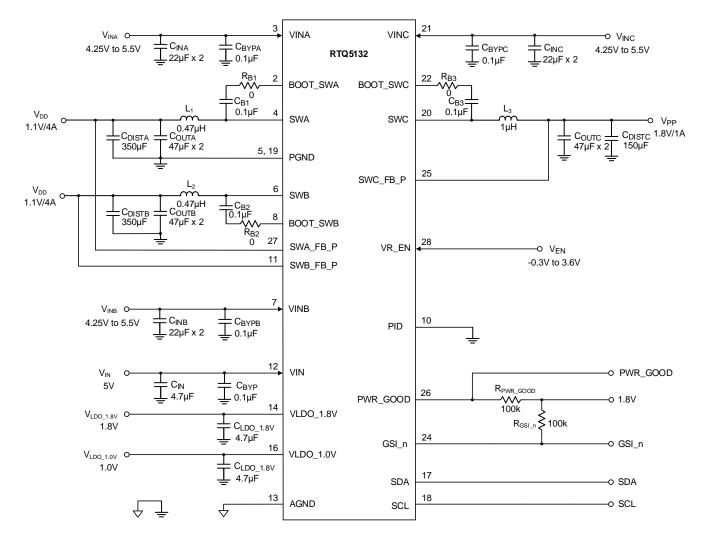

Figure 2. SWA and SWB are Operating in Single-Phase Mode

## **Table of Contents**

| 1  | Gener   | al Description1                      |    | 15.13  | Output Undervoltage and VIN_BULK     |     |

|----|---------|--------------------------------------|----|--------|--------------------------------------|-----|

| 2  | Orderi  | ng Information1                      |    |        | Undervoltage-Lockout Protection      | 43  |

| 3  | Markir  | ng Information1                      |    | 15.14  | Output Current Limiter Warning Event | 43  |

| 4  | Featur  | es1                                  |    | 15.15  | Output High Current Consumption      |     |

| 5  | Applic  | ations1                              |    |        | Warning Event                        | 44  |

| 6  | Simpli  | fied Application Circuit2            |    | 15.16  | PMIC High Temperature Warning and    |     |

| 7  | Pin Co  | onfiguration4                        |    |        | Critical Temperature Protection      | 45  |

| 8  | Functi  | onal Pin Description4                |    | 15.17  | Packet Error Code (PEC) and          |     |

| 9  | Functi  | onal Block Diagram6                  |    |        | Parity Error Event                   | 46  |

| 10 | Absol   | ute Maximum Ratings7                 |    | 15.18  | Output Regulator Control Topology    | 47  |

| 11 | Recon   | nmended Operating Conditions7        |    | 15.19  | Regulator Operating Mode Selection   | 48  |

| 12 | Electri | ical Characteristics8                |    | 15.20  | Analog-to-Digital Converter (ADC)    | 49  |

| 13 | Typica  | al Application Circuit14             |    | 15.21  | PMIC Address ID (PID)                | 51  |

|    | 13.1    | Recommended Component Selection for  |    | 15.22  | Error Injection                      | 51  |

|    |         | Typical Application Circuit16        | 16 | Applic | ation Information                    | 52  |

| 14 | Typica  | al Operating Characteristics17       |    | 16.1   | Inductor Selection                   | 52  |

| 15 | •       | tion24                               |    | 16.2   | Output Capacitor Selection           | 54  |

|    | 15.1    | PMIC Input Voltage Supply and Ramp   |    | 16.3   | Input Capacitor Selection            | 56  |

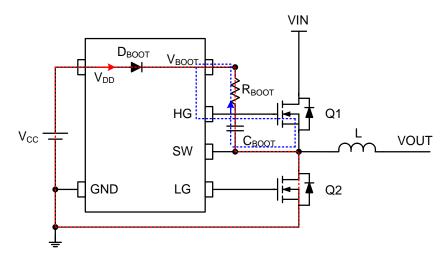

|    |         | Condition24                          |    | 16.4   | Bootstrap Circuit                    | 58  |

|    | 15.2    | Enabling PMIC Output Switch Voltage  |    | 16.5   | VLDO_1.8V and VLDO_1.0V Decoupling   |     |

|    |         | Regulators27                         |    |        | Capacitor                            | 60  |

|    | 15.3    | Secure Mode and Programmable Mode    |    | 16.6   | Thermal Consideration                | 60  |

|    |         | of Operation28                       |    | 16.7   | Layout Consideration                 |     |

|    | 15.4    | Power Down Output Regulators28       | 17 | Functi | ional Register Description           | 63  |

|    | 15.5    | PMIC Output Rail Off Timing31        |    | 17.1   | Register Attribute Definition        |     |

|    | 15.6    | GSI_n Signal32                       |    | 17.2   | Register Map Breakdown               |     |

|    | 15.7    | Power State Definition33             |    | 17.3   | Register Memory Protection           |     |

|    | 15.8    | Function Interrupts for PWR_GOOD and |    | 17.4   | B-5 Host Region Registers            |     |

|    |         | GSI_n Output Signals34               |    | 17.5   | DIMM Vendor Region Registers         | 106 |

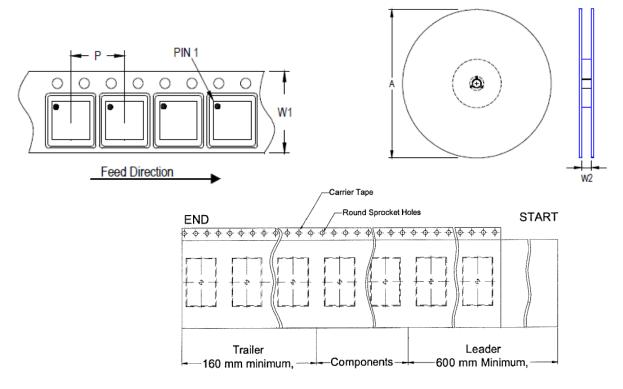

|    | 15.9    | Power-Good Signal39                  | 18 |        | e Dimension                          |     |

|    | 15.10   | Input Overvoltage Protection41       | 19 | -      | rint Information                     |     |

|    | 15.11   | Output Power-Good Status (SWA, SWB,  | 20 | Packir | ng Information                       |     |

|    |         | SWC, LDO_1.8V, and LDO_1.0V)41       |    | 20.1   | Tape and Reel Data                   |     |

|    | 15.12   | Output Overvoltage Protection (SWA,  |    | 20.2   | Tape and Reel Packing                |     |

|    |         | SWB, and SWC)42                      |    | 20.3   | Packing Material Anti-ESD Property   |     |

|    |         |                                      | 21 | Datasl | heet Revision History                | 124 |

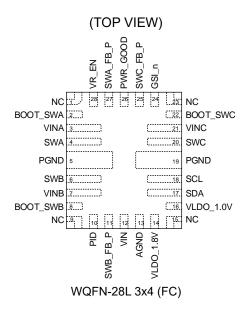

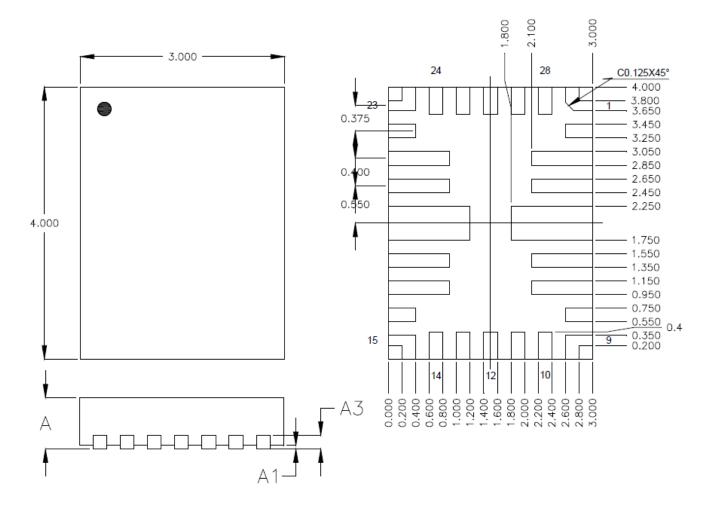

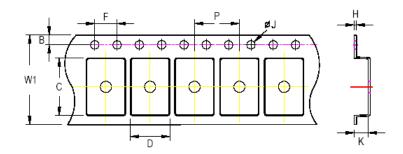

## 7 Pin Configuration

## **8 Functional Pin Description**

| Pin No. Pin Name |           | Pin Function                                                                                                                                                                                         |

|------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 9, 15, 23     | NC        | Non-functional pins. No internal connections to the chip.                                                                                                                                            |

| 2                | BOOT_SWA  | Buck A bootstrap. Bootstrap node for the switch node SWA high-side NMOS driver. Connect a capacitor between SWA and BOOT_SWA to form a floating supply across the high-side switch driver of buck A. |

| 3                | VINA      | Input supply of Buck A. VINA is connected to the 5V power plane on the DIMM. All three VINx input pins must be connected to 5V supply, even if one or more regulators are not intended to be used.   |

| 4                | SWA       | Buck A switch output. Output switch node of the SWA regulator. This pin is connected to an external inductor (L1).                                                                                   |

| 5, 19            | PGND      | Common Power ground. Connect PGND to the DIMM ground plane. PGND pins require special consideration during PCB layout.                                                                               |

| 6                | SWB       | Buck B switch output. Output switch node of the SWB regulator. This pin is connected to an external inductor (L2).                                                                                   |

| 7                | VINB      | Input supply of buck B. VINB is connected to the 5V power plane on the DIMM. All three VINx input pins must be connected to 5V supply, even if one or more regulators are not intended to be used.   |

| 8                | BOOT_SWB  | Buck B bootstrap. Bootstrap node for the switch node SWB high-side NMOS driver. Connect a capacitor between SWB and BOOT_SWB to form a floating supply across the high-side switch driver of buck B. |

| 10               | PID       | PMIC ID pin for I <sup>2</sup> C and I3C basic bus.                                                                                                                                                  |

| 11               | SWB_FB_P  | Positive feedback of buck B. This pin is connected to the SWB remote positive sense feedback.                                                                                                        |

| 12               | VIN       | 5V power input supply to the PMIC for analog circuits.                                                                                                                                               |

| 13               | AGND      | Analog ground. Connect AGND to the power ground pin with a single via.                                                                                                                               |

| 14               | VLDO_1.8V | PMIC 1.8V LDO supply. Connect a 4.7μF decoupling capacitor near this pin.                                                                                                                            |

| Pin No. | Pin Name  | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16      | VLDO_1.0V | PMIC 1.0V LDO supply for I3C push-pull driver. Connect a $4.7\mu F$ decoupling capacitor near this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 17      | SDA       | Bus data of I <sup>2</sup> C and I3C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 18      | SCL       | Bus clock of I <sup>2</sup> C and I3C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 20      | SWC       | Buck C switch output. Output switch node of the SWC regulator. This pin is connected to an external inductor (L3).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 21      | VINC      | Input supply of Buck C. VINC is connected to the 5V power plane on the DIMM. All three VINx input pins must be connected to 5V supply, even if one or more regulators are not intended to be used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 22      | BOOT_SWC  | Buck C bootstrap. Bootstrap node for the switch node SWC high-side NMOS driver. Connect a capacitor between SWC and BOOT_SWC to form a floating supply across the high-side switch driver of buck C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 24      | GSI_n     | General status interrupt. Open-Drain Output. The PMIC asserts this pin low to communicate one or more events to the host. This pin remains asserted until the appropriate registers are explicitly cleared and the event is no longer present.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 25      | SWC_FB_P  | Positive feedback of buck C. Switch node SWC remote positive sense feedback.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 26      | PWR_GOOD  | Power-good indicator. This pin can be configured as an open-drain output pin or as an input pin.  • As an open-drain output pin: The PMIC allows this pin to float high when the VIN_Bulk input supply, all enabled buck output regulators, and all LDO regulators maintain the tolerance thresholds configured in the appropriate registers. The PMIC drives this pin low if the VIN_Bulk input falls below the threshold, or if any of the enabled buck output regulators or any LDO output regulator exceeds the configured threshold tolerance.  • As an input pin: The PMIC disables its output regulators when this pin is driven low; however, the LDO outputs should remain on. |

| 27      | SWA_FB_P  | Positive feedback of buck A. This pin is connected to the SWA remote positive sense feedback.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 28      | VR_EN     | PMIC Enable. When this pin is high, the PMIC turns the regulator on. Conversely, when the pin is low, the PMIC turns the regulator off. This pin should not be left floating. If unused, it should be connected to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

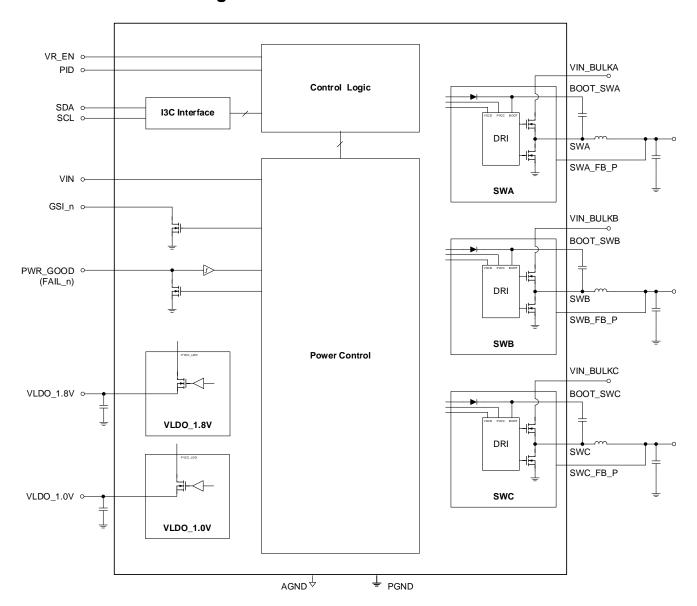

# 9 Functional Block Diagram

### 10 Absolute Maximum Ratings

### (Note 2)

| • Supply Input Voltage, VINA, VINB, VINC | 0.3V to 6V    |

|------------------------------------------|---------------|

| Supply Input Voltage, VIN                | 0.3V to 6V    |

| • AGND to PGND                           | 0.3V to 0.3V  |

| Switching PIN, SWA, SWB, SWC             |               |

| DC                                       | 0.3V to 6V    |

| < 25ns                                   | 3V to 9V      |

| Boot Voltage                             |               |

| BOOT to SWA (BOOT-SWA)                   | 0.3V to 6V    |

| BOOT to SWB (BOOT-SWB)                   | 0.3V to 6V    |

| BOOT to SWC (BOOT-SWC)                   | 0.3V to 6V    |

| • Other I/O                              | 0.3V to 6V    |

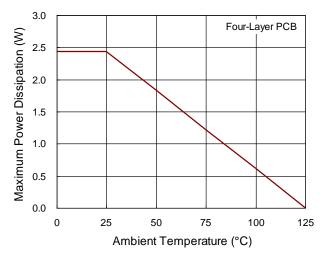

| • Power Dissipation, PD @ TA = 25°C      |               |

| WQFN-28L 3x4 (FC)                        | - 2.43W       |

| • Package Thermal Resistance (Note 3)    |               |

| WQFN-28L 3x4 (FC), θJA                   | - 41°C/W      |

| WQFN-28L 3x4 (FC), θJC                   | - 15.8°C/W    |

| WQFN-28L 3x4 (FC), θJB                   | - 8.38°C/W    |

| Lead Temperature (Soldering, 10 sec.)    | - 260°C       |

| Junction Temperature                     | 40°C to 155°C |

| Storage Temperature Range                | 55°C to 150°C |

| • ESD Susceptibility (Note 4)            |               |

| HBM                                      | - 2kV         |

| CDM                                      | - 500V        |

- **Note 2**. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 3.  $\theta_{JA}$  is measured under natural convection (still air) at  $T_A$  = 25°C with the component mounted on a high effective-thermal-conductivity four-layer test board on a JEDEC 51-7 thermal measurement standard.  $\theta_{JC}$  is measured at the bottom of the package.

- Note 4. Devices are ESD sensitive. Handling precautions are recommended.

## 11 Recommended Operating Conditions

### (Note 5)

| Supply Input Voltage, VINA, VINB, VINC | 4.25V to 5.5V |

|----------------------------------------|---------------|

| Supply Input Voltage, VIN              | 4.25V to 5.5V |

| Junction Temperature Range             | 10°C to 125°C |

| Ambient Temperature Range              | 0°C to 85°C   |

|                                        |               |

**Note 5**. The device is not guaranteed to function outside its operating conditions.

Copyright © 2024 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation

## 12 Electrical Characteristics

$(V_{IN\_SWA} = V_{IN\_SWB} = V_{IN\_SWC} = 5V, V_{IN} = 5V, T_A = -10^{\circ}C$  to  $105^{\circ}C$ , unless otherwise specified.)

| Parameter                                            | Symbol                 | Test Conditions                                                                                                          | Min  | Тур | Max  | Unit |  |

|------------------------------------------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------|------|-----|------|------|--|

| Input Supply Electrical Characteristics              |                        |                                                                                                                          |      |     |      |      |  |

| Bulk Input Supply<br>Voltage Ramp Up<br>Rate         | VIN_Bulk_<br>Ramp_Up   | The ramp up rate between 300 mV and 4.0V                                                                                 | 0.1  |     | 3    | V/ms |  |

| Bulk Input Supply<br>Voltage Ramp<br>Down Rate       | VIN_Bulk_<br>Ramp_Down | The ramp down rate between 4.0 V and 300mV.                                                                              | 0.5  |     | 1    | V/ms |  |

| (VIN)<br>Shutdown Current                            | ISHDN_VIN              | T <sub>A</sub> = 25°C; VIN = VIN_Bulk = 5V,<br>VR_EN = 0, All circuitry including<br>output regulators and LDOs are off. |      |     | 25   | μА   |  |

| VIN<br>Supply Current<br>(Non-Switching)             | I <sub>Q_VIN_NSW</sub> | T <sub>A</sub> = 25°C; I <sub>OUT</sub> = 0mA, all LDO,<br>SWA to SWC on, no switching                                   |      | 1.9 | 1    | mA   |  |

| VIN Undervoltage-                                    | Lockout and O\         | /P Threshold                                                                                                             |      |     |      |      |  |

| VIN<br>Undervoltage-<br>Lockout Rising<br>Threshold  | Vin_uvlo_r             | Rising edge                                                                                                              |      | 4   |      | V    |  |

| VIN<br>Undervoltage-<br>Lockout Falling<br>Threshold | VIN_UVLO_F             | Falling edge                                                                                                             |      | 3.8 |      | V    |  |

| VIN Overvoltage<br>Rising Threshold                  | VIN_OVP_R              | Setting by reg_0x1B"[7] = "0"                                                                                            |      | 6   | -    | V    |  |

| I <sup>2</sup> C, I3C and Interfa                    | ace DC Electrica       | l Specification                                                                                                          |      |     |      |      |  |

| SDA, SCL I <sup>2</sup> C<br>Operate<br>Frequency    | fscl_i2C               |                                                                                                                          | 0.01 |     | 1    | MHz  |  |

| SDA, SCL I3C<br>Operate<br>Frequency                 | fscl_i3c               |                                                                                                                          | 0.01 | 1   | 12.5 | MHz  |  |

| SDA, SCL Input<br>High Voltage                       | V <sub>IH_I2C</sub>    |                                                                                                                          | 0.7  |     | 3.6  | V    |  |

| SDA, SCL Input<br>Low Voltage                        | V <sub>IL_I2C</sub>    |                                                                                                                          | -0.3 |     | 0.3  | V    |  |

| PWR_GOOD Input High Voltage                          | VIH_PGOOD              |                                                                                                                          | 1.26 |     | 3.6  | V    |  |

| VR_EN Input High Voltage                             | VIH_EN                 |                                                                                                                          | 1.26 |     | 3.6  | V    |  |

| PWR_GOOD<br>Input Low Voltage                        | VIL_PGOOD              |                                                                                                                          | -0.3 |     | 0.3  | V    |  |

| VR_EN Input Low<br>Voltage                           | VIL_EN                 |                                                                                                                          | -0.3 |     | 0.3  | V    |  |

| PID Input High<br>Voltage                            | VIH_PID                |                                                                                                                          | 1.2  |     |      | V    |  |

| Parameter                                          | Symbol                                     | Test Conditions                        | Min       | Тур    | Max   | Unit                |  |  |

|----------------------------------------------------|--------------------------------------------|----------------------------------------|-----------|--------|-------|---------------------|--|--|

| PID Input Low<br>Voltage                           | VIL_PID                                    |                                        |           |        | 0.2   | V                   |  |  |

| SDA Output High<br>Voltage                         | Voh_sda                                    | I <sub>o</sub> = -3mA                  | 0.75      |        |       | V                   |  |  |

| (SDA, GSI_n,<br>PWR_GOOD)<br>Output Low<br>Voltage | VoL                                        | I <sub>o</sub> = 3mA                   | I         | I      | 0.3   | V                   |  |  |

| SDA Output High<br>Current                         | IOH_SDA                                    |                                        | -3        |        |       | mA                  |  |  |

| (SDA, GSI_n,<br>PWR_GOOD<br>Output Low<br>Current  | loL                                        |                                        | 1         | 1      | 3     | mA                  |  |  |

| SDA Output Pull-<br>Up Impedance                   | Rpu_sda                                    |                                        | -         | 40     |       | Ω                   |  |  |

| SDA Output Pull-<br>Down Impedance                 | RPD_SDA                                    |                                        | 1         | 20     |       | Ω                   |  |  |

| GSI_n Output<br>Pull-Down<br>Impedance             | RPD_GSI_n                                  |                                        | 1         | 50     |       | Ω                   |  |  |

| PWR_GOOD<br>Output Pull-Down<br>Impedance          | RPD_PGOOD                                  |                                        |           | 50     |       | Ω                   |  |  |

| SWA/SWB Rail – V                                   | /DD/VDDQ (1.1V)                            | ) - Single Phase Regulator (0.8V to 1. | 435V, ITD | CA/B = | 4A/4A |                     |  |  |

| Output Voltage<br>Setting                          | Vout                                       | SWAB setting by reg_0x21"[7:1]         | 0.8       |        | 1.435 | V                   |  |  |

| Output Voltage<br>Accuracy                         | Vout_ab_acc                                | IOUT = 0A, operating at CCM            | -0.75     |        | 0.75  | % of<br>Vout_<br>AB |  |  |

| VID Slew Rate                                      | SRVID_AB                                   |                                        |           | 1      |       | mV/<br>μs           |  |  |

| SWA/SWB Soft-St                                    | art/Soft-Stop Tim                          | 1e                                     |           |        |       |                     |  |  |

| Soft-Start Time                                    | t <sub>SS</sub>                            | t <sub>set</sub> = 1ms to 14ms         | -15       |        | 15    | % of<br>tss         |  |  |

| Soft-Stop Time                                     | t <sub>STOP</sub>                          | t <sub>set</sub> = 0.5ms to 4ms        | -20       |        | 20    | % of<br>tstop       |  |  |

| SWA/SWB Interna                                    | SWA/SWB Internal MOSFET Turn On Resistance |                                        |           |        |       |                     |  |  |

| On-Resistance of<br>High-Side<br>MOSFET            | RDSON_H                                    | T <sub>A</sub> = 25°C                  |           | 16     |       | mΩ                  |  |  |

| On-Resistance of<br>Low-Side<br>MOSFET             | RDSON_L                                    | T <sub>A</sub> = 25°C                  |           | 10     |       | mΩ                  |  |  |

Copyright © 2024 Richtek Technology Corporation. All rights reserved.

| Parameter Symbol                                |                                 | Test Conditions                                          | Min    | Тур  | Max    | Unit                |  |

|-------------------------------------------------|---------------------------------|----------------------------------------------------------|--------|------|--------|---------------------|--|

| SWA/SWB Switch                                  | ing Frequency                   |                                                          |        |      |        |                     |  |

|                                                 |                                 | Setting by reg_0x29"[5:4]/0x2A"[7:6]<br>= "00" (default) | 0.6375 | 0.75 | 0.8625 |                     |  |

| Switching                                       | f <sub>SW AB</sub>              | Setting by reg_0x29"[5:4]/0x2A"[7:6]<br>= "01"           | 0.85   | 1    | 1.15   |                     |  |

| Frequency                                       | ISW_AB                          | Setting by reg_0x29"[5:4]/0x2A"[7:6]<br>= "10"           | 1.0625 | 1.25 | 1.4375 | MHz                 |  |

|                                                 |                                 | Setting by reg_0x29"[5:4]/0x2A"[7:6]<br>= "11"           | 1.275  | 1.5  | 1.725  |                     |  |

| SWA/SWB Power-                                  | Good Indicator                  |                                                          |        |      |        |                     |  |

| (Power Good)                                    | V <sub>OUT_AB_PG</sub>          | Setting by reg_0x21"[0]/0x25"[0] = "0" (default)         |        | -5   |        | % of                |  |

| Falling Threshold                               | OOD_F                           | Setting by reg_0x21"[0]/0x25"[0] = "1"                   |        | -7.5 |        | VOUT_<br>AB         |  |

| (Power Good)<br>Falling<br>Propagation<br>Delay | t <sub>DLY_PGOOD_</sub><br>F_AB |                                                          |        | 5    |        | μS                  |  |

|                                                 | Vout_ab_pg<br>ood_r             | Setting by reg_0x22"[7:6]/0x26"[7:6]<br>= "00"           |        | 5    |        |                     |  |

| (Power Good)                                    |                                 | Setting by reg_0x22"[7:6]/0x26"[7:6]<br>= "01" (default) |        | 7.5  |        | % of<br>VOUT_<br>AB |  |

| Rising Threshold                                |                                 | Setting by reg_0x22"[7:6]/0x26"[7:6]<br>= "10"           |        | 10   |        |                     |  |

|                                                 |                                 | Setting by reg_0x22"[7:6]/0x26"[7:6]<br>= "11"           |        | 2.5  |        |                     |  |

| (Power Good)<br>Rising<br>Propagation<br>Delay  | t <sub>DLY_PGOOD_</sub><br>R_AB |                                                          |        | 5    |        | μs                  |  |

| SWA/SWB Protec                                  | tions                           |                                                          |        |      |        |                     |  |

|                                                 |                                 | Setting by reg_0x22"[5:4]/0x26"[5:4]<br>= "00"           |        | 7.5  |        |                     |  |

| Output<br>Overvoltage                           | V <sub>OUT_AB_OVP</sub>         | Setting by reg_0x22"[5:4]/0x26"[5:4]<br>= "01"           |        | 10   |        | % of<br>Vout        |  |

| Rising Threshold                                | _R                              | Setting by reg_0x22"[5:4]/0x26"[5:4]<br>= "10" (default) |        | 12.5 |        | AB                  |  |

|                                                 |                                 | Setting by reg_0x22"[5:4]/0x26"[5:4]<br>= "11"           |        | 20   |        |                     |  |

| Output Overvoltage Protection Propagation Delay | t <sub>DLY_OVP_AB</sub>         |                                                          |        | 5    |        | μs                  |  |

| Parameter                                        | Symbol                   | Test Conditions                                                  |       | Тур   | Max   | Unit               |  |

|--------------------------------------------------|--------------------------|------------------------------------------------------------------|-------|-------|-------|--------------------|--|

|                                                  | Vout_ab_uvp              | Setting by reg_0x22"[3:2]/0x26"[3:2]<br>= "00" (default)         |       | -10   |       |                    |  |

| Output                                           |                          | Setting by reg_0x22"[3:2]/0x26"[3:2]<br>= "01"                   |       | -12.5 |       | % of               |  |

| Undervoltage<br>Falling Threshold                | _F                       | Setting by reg_0x22"[3:2]/0x26"[3:2]<br>= "10"                   | -     | -7.5  | -     | Vout_<br>ab        |  |

|                                                  |                          | Setting by reg_0x22"[3:2]/0x26"[3:2]<br>= "11"                   | -     | -20   | -     |                    |  |

| Output Undervoltage Protection Propagation Delay | t <sub>DLY_UVP_</sub> AB |                                                                  | ŀ     | 5     | ŀ     | μs                 |  |

| SWA/SWB Curren                                   | t Limit                  |                                                                  |       |       |       |                    |  |

|                                                  |                          | Valley current limited<br>Setting by reg_0x20"[7:6]/[3:2] = "00" |       | 3     |       |                    |  |

| 0                                                | ILIM_SWA/B               | Setting by reg_0x20"[7:6]/[3:2] = "01"                           |       | 3.5   |       | - A                |  |

| Current Limit                                    |                          | Setting by reg_0x20"[7:6]/[3:2] = "10"                           |       | 4     |       |                    |  |

|                                                  |                          | Setting by reg_0x20"[7:6]/[3:2] = "11" (default)                 |       | 4.5   | ŀ     |                    |  |

| SWC Rail - VPP (1                                | I.8V) – Single Ph        | ase Regulator (1.5V to 2.135V, ITDC =                            | = 1A) |       |       |                    |  |

| Output Voltage<br>Setting                        | Vout_c                   | Setting by reg_0x27"[7:1]                                        | 1.5   | 1.8   | 2.135 | V                  |  |

| Output Voltage<br>Accuracy                       | Vout_c_acc               | IOUT = 0A, operating at CCM                                      | -0.75 |       | 0.75  | % of<br>Vout_<br>C |  |

| VID Slew Rate                                    | SR <sub>VID_C</sub>      |                                                                  |       | 1     |       | mV/μs              |  |

| SWC Soft-Start/So                                | oft-Stop Time            |                                                                  |       |       |       |                    |  |

| Soft-Start Time                                  | t <sub>SS</sub>          | t <sub>set</sub> = 1ms to 14ms                                   | -15   |       | 15    | % of<br>tss        |  |

| Soft-Stop Time                                   | t <sub>STOP</sub>        | t <sub>set</sub> = 1ms to 8ms                                    | -20   |       | 20    | % of<br>tstop      |  |

| SWC Internal MOSFET Turn On Resistance           |                          |                                                                  |       |       |       |                    |  |

| On-Resistance of<br>High-Side<br>MOSFET          | RDSON_H                  | TA = 25°C                                                        |       | 55    |       | mΩ                 |  |

| On-Resistance of<br>Low-Side<br>MOSFET           | RDSON_L                  | Ta = 25°C                                                        |       | 45    |       | mΩ                 |  |

| Parameter                                       | Symbol                         | Test Conditions                            | Min    | Тур   | Max    | Unit               |  |

|-------------------------------------------------|--------------------------------|--------------------------------------------|--------|-------|--------|--------------------|--|

| SWC Switching F                                 | requency                       |                                            |        |       | •      | •                  |  |

|                                                 |                                | Setting by reg_0x2A"[1:0] = "00"           | 0.6375 | 0.75  | 0.8625 | MHz                |  |

| Switching                                       | fsw c                          | Setting by reg_0x2A"[1:0] = "01" (default) | 0.85   | 1     | 1.15   |                    |  |

| Frequency                                       | _                              | Setting by reg_0x2A"[1:0] = "10"           | 1.0625 | 1.25  | 1.4375 |                    |  |

|                                                 |                                | Setting by reg_0x2A"[1:0] = "11"           | 1.275  | 1.5   | 1.725  |                    |  |

| SWC Power-Good                                  | I Indicator                    |                                            |        |       |        |                    |  |

| (Power Good)                                    | V <sub>OUT_C_PGO</sub>         | Setting by reg_0x27"[0] = "0" (default)    |        | -5    |        | % of<br>Vout       |  |

| Falling Threshold                               | OD_F                           | Setting by reg_0x27"[0] = "1"              |        | -7.5  |        | C                  |  |

| (Power Good) Falling Propagation Delay          | t <sub>DLY_PGOOD_</sub><br>F_C |                                            |        | 5     |        | μS                 |  |

|                                                 | Vout_c_pgo                     | Setting by reg_0x28"[7:6] = "00"           |        | 5     |        | % of<br>Vout_<br>c |  |

| (Power Good)                                    |                                | Setting by reg_0x28"[7:6] = "01" (default) |        | 7.5   |        |                    |  |

| Rising Threshold                                | OD_R                           | Setting by reg_0x28"[7:6] = "10"           |        | 10    |        |                    |  |

|                                                 |                                | Setting by reg_0x28"[7:6] = "11"           |        | 2.5   |        |                    |  |

| (Power Good) Rising Propagation Delay           | t <sub>DLY_PGOOD_</sub><br>R_C |                                            |        | 5     |        | μS                 |  |

| SWC Protections                                 |                                |                                            |        |       |        |                    |  |

|                                                 |                                | Setting by reg_0x28"[5:4] = "00"           |        | 7.5   |        |                    |  |

| Output                                          | V <sub>OUT_C_OVP_</sub>        | Setting by reg_0x28"[5:4] = "01"           |        | 10    |        | % of               |  |

| Overvoltage<br>Rising Threshold                 | R                              | Setting by reg_0x28"[5:4] = "10" (default) |        | 12.5  |        | Vout_<br>c         |  |

|                                                 |                                | Setting by reg_0x28"[5:4] = "11"           |        | 20    |        |                    |  |

| Output Overvoltage Protection Propagation Delay | t <sub>DLY_OVP_C</sub>         |                                            |        | 5     |        | μs                 |  |

|                                                 |                                | Setting by reg_0x28"[3:2] = "00" (default) |        | -10   |        |                    |  |

| Output<br>Undervoltage                          | V <sub>OUT_C_UVP_</sub>        | Setting by reg_0x28"[3:2] = "01"           |        | -12.5 |        | % of<br>Vout_<br>C |  |

| Falling Threshold                               | F                              | Setting by reg_0x28"[3:2] = "10"           |        | -7.5  |        |                    |  |

|                                                 |                                | Setting by reg_0x28"[3:2] = "11"           |        | -20   |        | 1                  |  |

| Parameter                                        | Symbol                                | Test Conditions                                                          | Min  | Тур  | Max  | Unit |

|--------------------------------------------------|---------------------------------------|--------------------------------------------------------------------------|------|------|------|------|

| Output Undervoltage Protection Propagation Delay | t <sub>DLY_UVP_</sub> C               |                                                                          |      | 5    |      | μs   |

| SWC Current Limi                                 | t                                     |                                                                          |      |      |      |      |

| - ···                                            |                                       | For Low Current, valley current limited Setting by reg_0x20"[1:0] = "00" |      | 0.5  |      |      |

| Positive Inductor Valley Current                 | ILIM VALLEY C                         | Setting by reg_0x20"[1:0] = "01"                                         |      | 1.0  |      | Α    |

| Limit                                            |                                       | Setting by reg_0x20"[1:0] = "10"                                         |      | 1.5  |      |      |

|                                                  |                                       | Setting by reg_0x20"[1:0] = "11" (default)                               |      | 2.0  |      |      |

| VLDO_1.8V (1.8V,                                 | IMAX = 25mA)                          |                                                                          |      |      |      |      |

|                                                  |                                       | Setting by reg_0x2B"[7:6] = "00"                                         | 1.66 | 1.7  | 1.74 |      |

| Output Voltage                                   | VLDO 1.8V                             | Setting by reg_0x2B"[7:6] = "01" (default)                               | 1.76 | 1.8  | 1.84 | V    |

|                                                  | _                                     | Setting by reg_0x2B"[7:6] = "10"                                         | 1.85 | 1.9  | 1.95 |      |

|                                                  |                                       | Setting by reg_0x2B"[7:6] = "11"                                         | 1.95 | 2.0  | 2.05 |      |

| Soft-Start Time                                  | t <sub>SS</sub>                       |                                                                          |      | 0.25 |      | ms   |

| (Power Good)<br>Rising Threshold                 | V <sub>LDO_1.8</sub> V_PG<br>OOD_R    | Setting by reg_0x1A"[2] = "0"                                            |      | 1.6  |      | V    |

| (Power Good)<br>Rising<br>Propagation<br>Delay   | t <sub>DLY_PGOOD_</sub><br>R_LDO_1.8V |                                                                          |      | 5    |      | μs   |

| Current Limit                                    | ILIM_LDO_1.8V                         |                                                                          | 50   |      |      | mA   |

| VLDO_1.0V (1.0V,                                 | IMAX = 20mA)                          |                                                                          |      |      |      |      |

|                                                  |                                       | Setting by reg_0x2B"[2:1] = "00"                                         | 0.88 | 0.9  | 0.92 |      |

| Output Voltage                                   | VLDO 1.0V                             | Setting by reg_0x2B"[2:1] = "01" (default)                               | 0.98 | 1.0  | 1.02 | V    |

|                                                  | _                                     | Setting by reg_0x2B"[2:1] = "10"                                         | 1.08 | 1.1  | 1.12 |      |

|                                                  |                                       | Setting by reg_0x2B"[2:1] = "11"                                         | 1.18 | 1.2  | 1.22 |      |

| Soft-Start Time                                  | t <sub>SS</sub>                       |                                                                          |      | 0.12 |      | ms   |

| (Power Good)                                     | V <sub>LDO_1.0</sub> V_PG             | Setting by reg_0x1A"[0] = "0" (default)                                  |      | -10  |      | % of |

| Rising Threshold                                 | OOD_R                                 | Setting by reg_0x1A"[0] = "1"                                            |      | -15  |      | VLDO |

| (Power Good)<br>Rising<br>Propagation<br>Delay   | t <sub>DLY_PGOOD_</sub><br>R_LDO_1.0V |                                                                          |      | 5    |      | μs   |

| Current Limit                                    | ILIM_LDO_1.0V                         |                                                                          | 50   |      |      | mA   |

Copyright © 2024 Richtek Technology Corporation. All rights reserved.

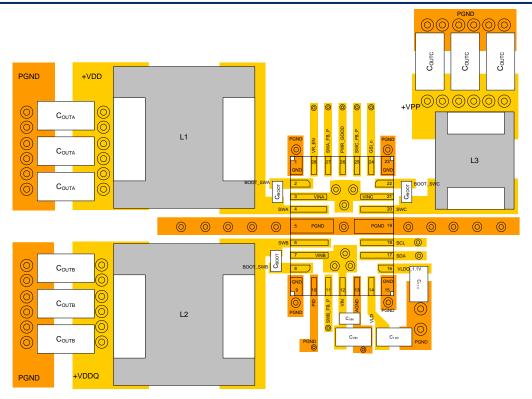

# 13 Typical Application Circuit

Figure 3. Typical Application Circuit When SWA and SWB Are Combined as Two-Phase, Single-Output Rail.

Figure 4. Typical Application Circuit When SWA and SWB Are Separated for Two Outputs.

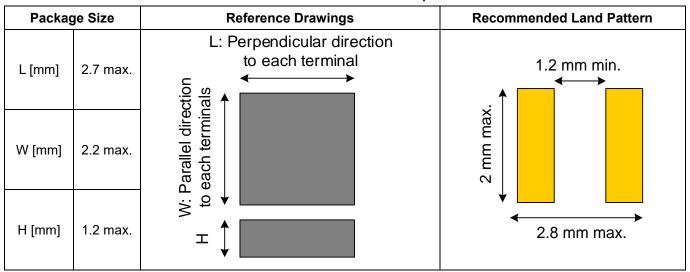

### 13.1 Recommended Component Selection for Typical Application Circuit

**Suggested Components for SWA and SWB**

| ouggottu componente les estricula esta |           |                 |                              |  |  |  |

|----------------------------------------|-----------|-----------------|------------------------------|--|--|--|

| Component                              | Value     | Physical Size   | Part No.                     |  |  |  |

| L1, L2                                 | 0.47μΗ    | 3.2 x 2.5 x 1.2 | HTTD32251BR47MMR/GLVQMR4701A |  |  |  |

| L1, L2                                 | 0.68μΗ    | 3.2 x 2.5 x 1.2 | HTTD32251BR68MMR/GLVQMR6801A |  |  |  |

| Свурх                                  | 0.1μF     | 10V; 0201       | GRM033C81E104KE14            |  |  |  |

| CINX                                   | 22μF (x2) | 10V; 0603       | GRM188R61A226ME15            |  |  |  |

| Соитх                                  | 47μF (x2) | 6.3V; 0603      | GRM188R60J476ME01            |  |  |  |

**Suggested Components for SWC**

| Component | Value     | Physical Size   | Part No.                                     |  |  |  |

|-----------|-----------|-----------------|----------------------------------------------|--|--|--|

| L3        | 1.0μΗ     | 2.5 x 2.0 x 1.2 | HTTD25201B1R0MSR/GLULM1R001A/DFE252012P-1R0M |  |  |  |

| L3        | 1.5μΗ     | 2.5 x 2.0 x 1.2 | HTTD25201B1R5MSR/GLULM1R501A/MEMK2520D1R5ML  |  |  |  |

| Свурс     | 0.1μF     | 10V; 0201       | GRM033C81E104KE14                            |  |  |  |

| CINC      | 22μF (x2) | 10V; 0603       | GRM188R61A226ME15                            |  |  |  |

| Соитс     | 47μF (x2) | 6.3V; 0603      | GRM188R60J476ME01                            |  |  |  |

Suggested Components for VLDO\_1.8V and VLDO\_1.0V

| Component | Value | Physical Size | Part No.          |

|-----------|-------|---------------|-------------------|

| Свур      | 0.1μF | 10V; 0201     | GRM033C81E104KE14 |

| Cin       | 4.7μF | 10V; 0402     | GRM155R61A475MEAA |

| CLDO_1.8V | 4.7μF | 6.3V; 0402    | GRM155R60J475ME47 |

| CLDO_1.0V | 4.7μF | 6.3V; 0402    | GRM155R60J475ME47 |

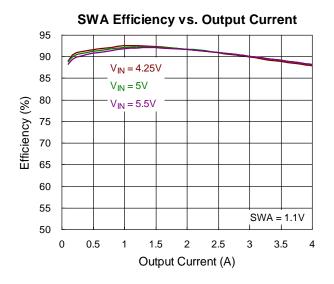

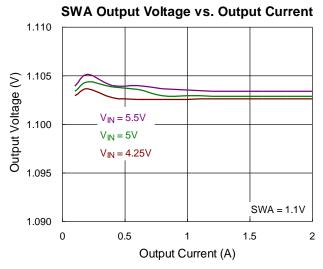

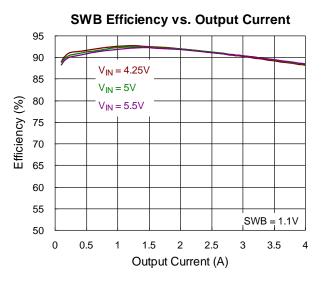

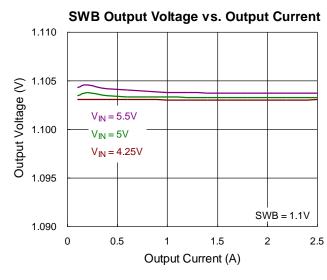

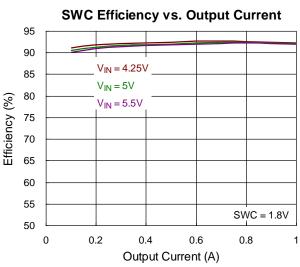

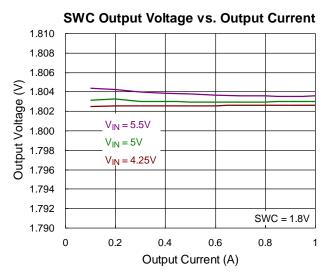

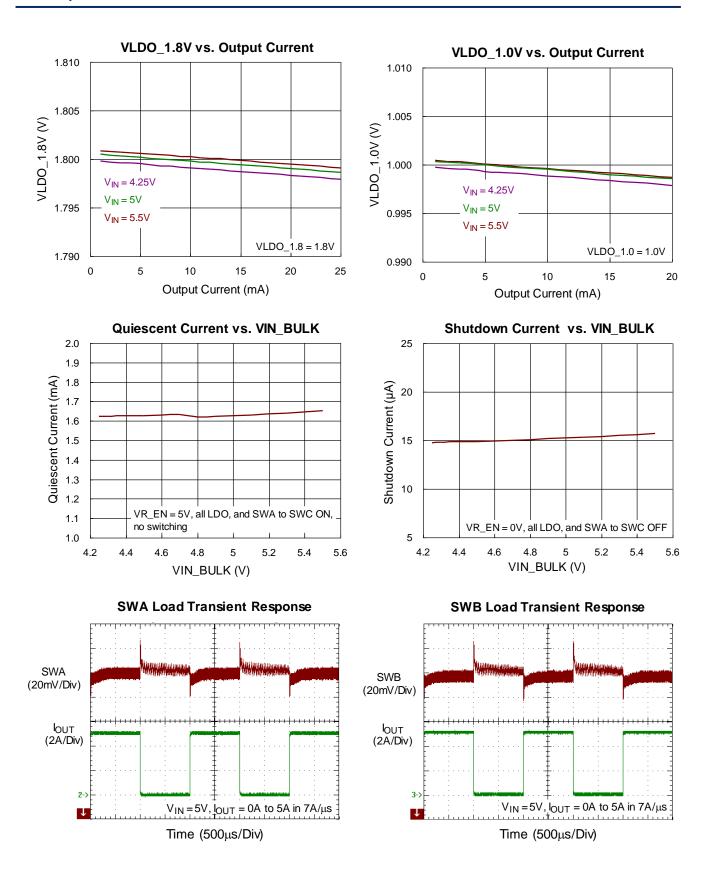

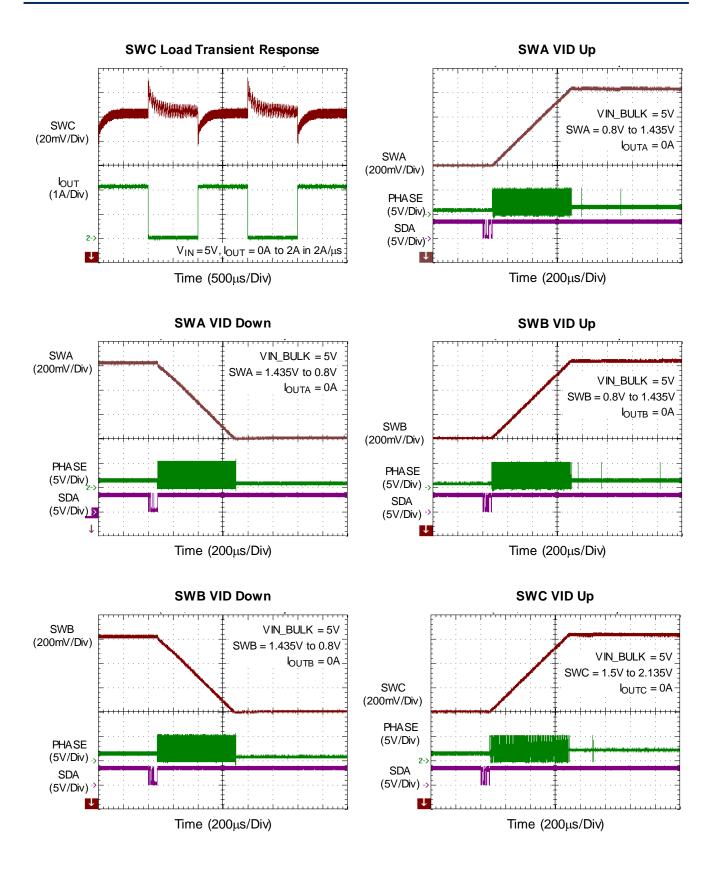

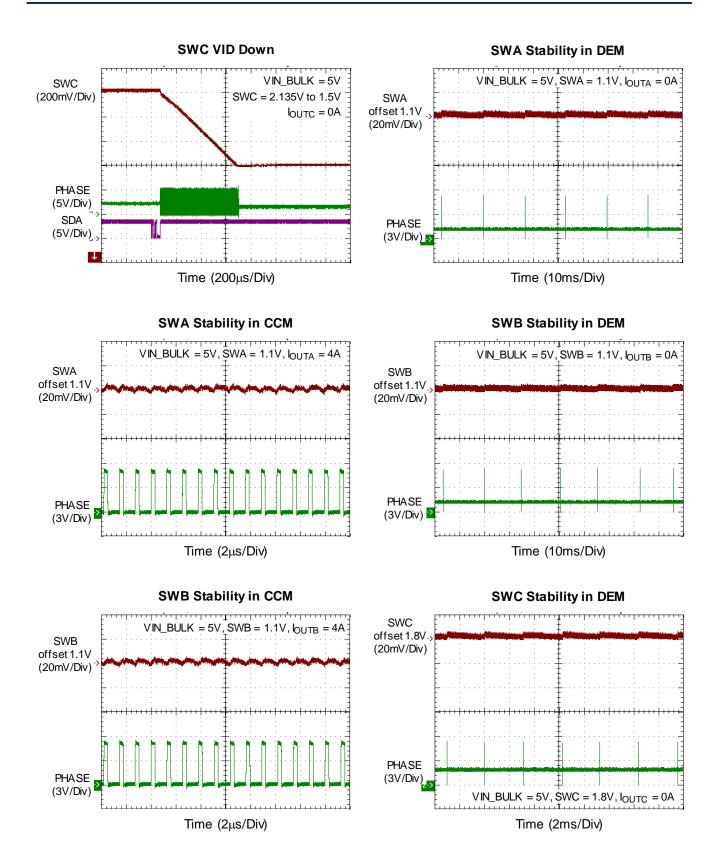

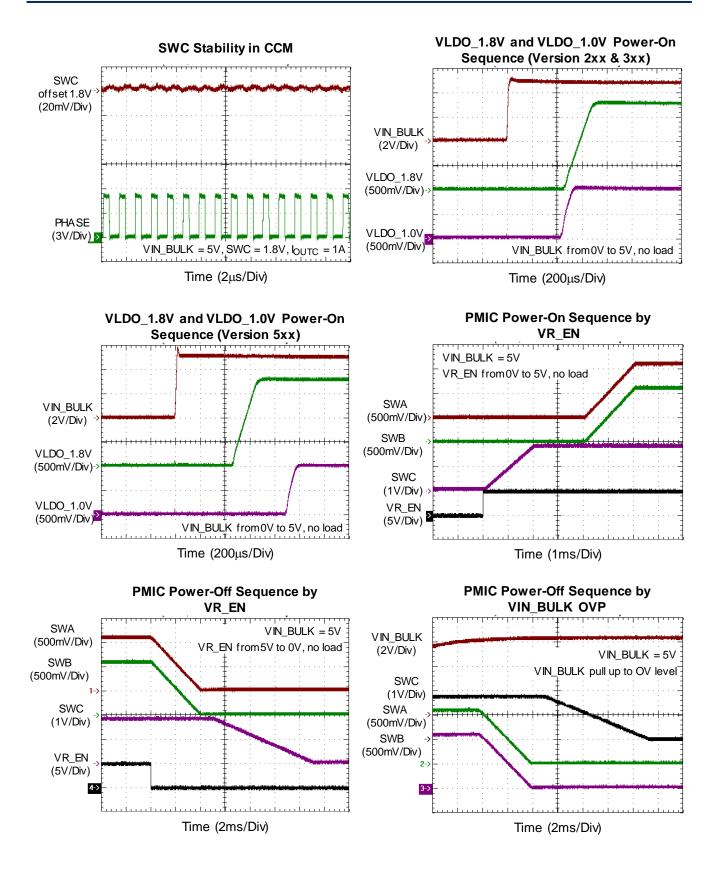

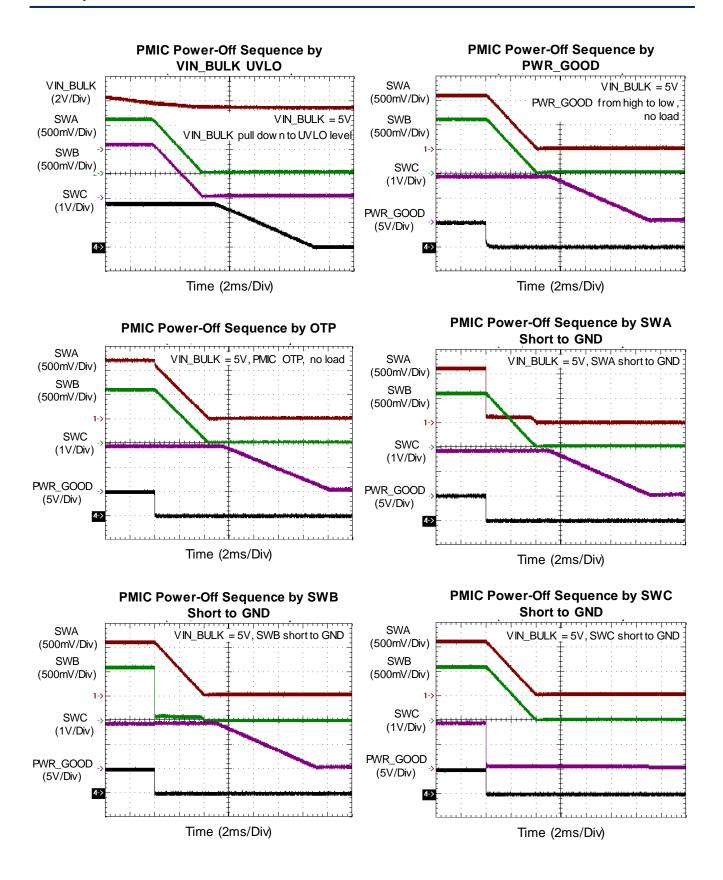

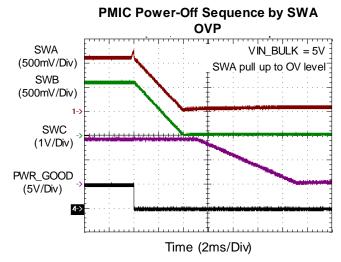

## 14 Typical Operating Characteristics

Copyright © 2024 Richtek Technology Corporation. All rights reserved.

Copyright © 2024 Richtek Technology Corporation. All rights reserved.

2024

Copyright © 2024 Richtek Technology Corporation. All rights reserved.

Copyright © 2024 Richtek Technology Corporation. All rights reserved.

### 15 Operation

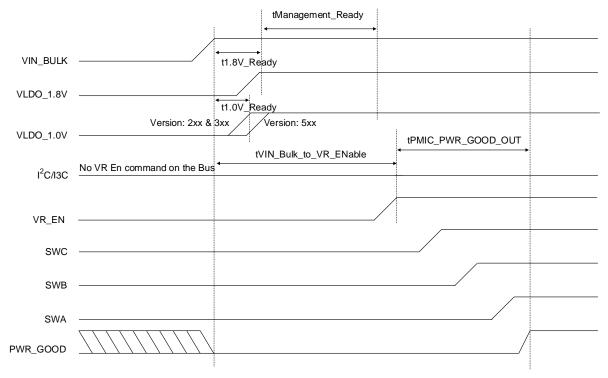

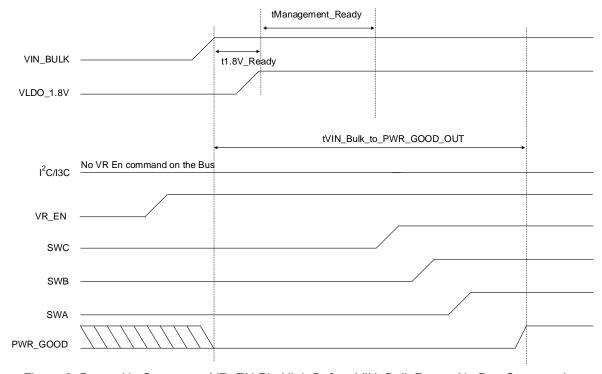

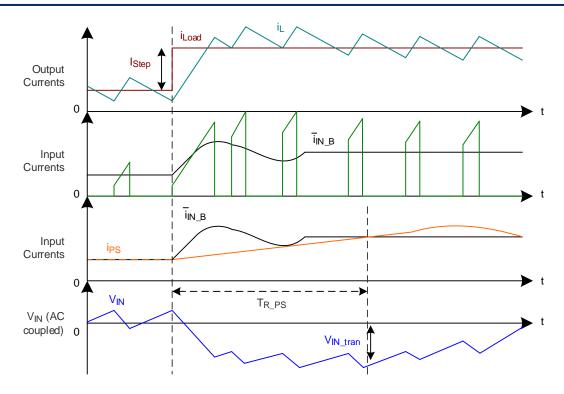

### 15.1 PMIC Input Voltage Supply and Ramp Condition

The VIN Bulk supply is used by the RTQ5132 for all three switch (SWA, SWB, and SWC) output regulators and two LDO output (VLDO 1.8V and VLDO 1.0V) regulators. Note that the VLDO 1.8V LDO output is separate and independent from the SWC output, which is for the DRAM VPP rail. The VLDO 1.0V LDO output is separate and independent from SWA or SWB.

At the first power-on, the VIN Bulk input supply should reach a minimum threshold voltage of 4.25V before it can be detected as a valid input supply by the RTQ5132.

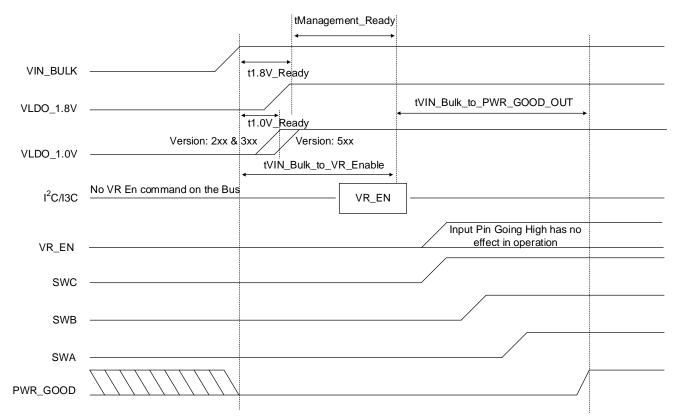

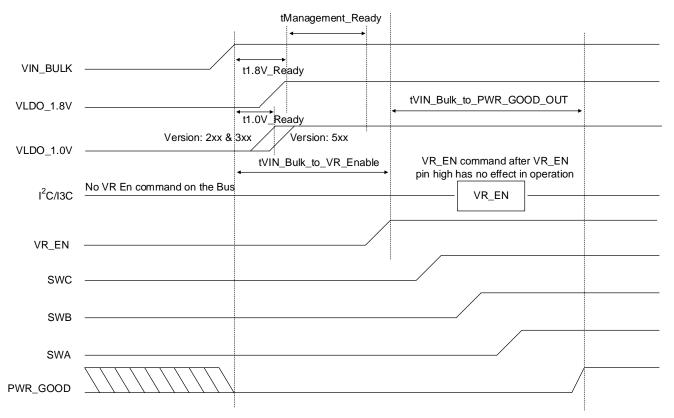

Once the VIN Bulk supply is valid and stable, the RTQ5132 should assert the PWR GOOD output low and drive VLDO\_1.8V and VLDO\_1.0V supplies within t1.8V\_Ready (typically 500μs) and t1.0V\_Ready (typically 500μs) time, respectively. The RTQ5132 only drives the PWR\_GOOD output signal low when the VIN\_Bulk input supply reaches a minimum of 4.25V. The PWR\_GOOD output is pulled up to either 1.8V or 3.3V on the platform or the host controller.

The PWR GOOD pull-up voltage (either 1.8V or 3.3V) is available before or after the VIN Bulk is valid and stable. If the PWR\_GOOD pull-up voltage is available before the VIN\_Bulk is applied, the PWR\_GOOD signal is high. When the VIN\_Bulk is applied to the RTQ5132, the RTQ5132 asserts the PWR\_GOOD output low.

The RTQ5132 should enable the  $I^2C/I3C$  bus interface function within tManagement\_Ready (maximum = 3ms). The user should not attempt to access the RTQ5132's memory registers until the tManagement\_Ready timing requirement is satisfied.

During power-on, the user should:

- 1. Ramp up the VIN\_BULK supply.

- 2. Hold the VIN Bulk supply stable for a minimum of tVIN Bulk to VR Enable time (minimum = 6.5ms).

- 3. Keep the VR\_EN pin static, either low or high.

- 4. If the VR EN signal is held low during the VIN Bulk ramp, it may transition to high only once. Once high, it should remain high. The VR\_EN signal is not allowed to transition to low during the VIN\_Bulk ramp-up.

- 5. If the VR\_EN pin is held high during the VIN\_Bulk ramp-up, or transitions to high, the RTQ5132 turns on its output rails.

- 6. If the VR EN pin is held low during the VIN Bulk ramp, assert the VR EN signal high to turn on the RTQ5132 output rails. Alternatively, the user can issue a VR Enable command by setting the register, Register 0x32[7] = 1, via I<sup>2</sup>C/I3C basic bus or via DEVCTRL CCC to turn on the RTQ5132 output rails.

Figure 6 to Figure 8 show examples of the PMIC power-up initialization sequence. Note that the specific sequence of ramping the output regulators (SWA, SWB, and SWC) is for example purposes only. The specific ramp-up sequence is configurable through power-on sequence configuration registers.

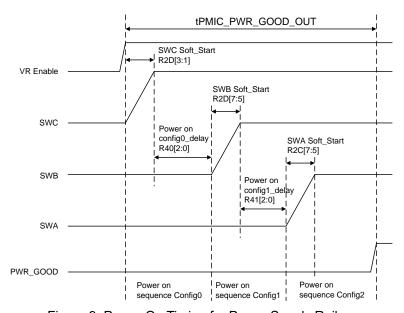

After the VR Enable command is registered on the I<sup>2</sup>C or I3C basic bus, or the VR EN pin is registered high, the RTQ5132 should complete the following steps within tPMIC\_PWR\_GOOD\_OUT:

- 1. Check that the VIN Bulk Power-Good status is valid.

- 2. Power up itself the RTQ5132 executes Power-On Sequence Config0 to Power-On Sequence Config2 registers and configures its internal registers as programmed in the DIMM vendor's memory space registers.

- 3. Power up all enabled output switch regulators and prepare for normal operation.

- 4. Update status registers "Register 0x08" [5,3:2] and float the PWR GOOD signal within a maximum of the tPMIC\_PWR\_GOOD\_OUT time.

If the RTQ5132's PWR GOOD signal is not floated within the tPMIC PWR GOOD OUT time, the user can

access the RTQ5132 status registers for detailed information after the tPMIC\_PWR\_GOOD\_OUT time. The RTQ5132 may issue a NACK (Negative-Acknowledge) to any host request on the I<sup>2</sup>C or I3C basic bus after the VR Enable command (either with the VR\_EN pin set high or via the I2C/I3C basic bus) until the tPMIC\_PWR\_GOOD\_OUT time expires.

Figure 5. Power-Up Sequence; VR\_EN Pin High After VIN\_Bulk Ramp; No Bus Command

Figure 6. Power-Up Sequence; VR\_EN Pin High Before VIN\_Bulk Ramp; No Bus Command

DSQ5132-07 October 2024 www.richtek.com

Copyright © 2024 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation

Figure 7. PMIC Power Up Sequence with VR\_EN Pin Followed by Bus Command

Figure 8. PMIC Power-Up Sequence with VR\_EN Pin Followed by Bus Command

DSQ5132-07

### 15.2 Enabling PMIC Output Switch Voltage Regulators

<u>Figure 9</u> illustrates the timing relationship when the RTQ5132 receives a VR Enable command (either via the VR\_EN pin or on the I<sup>2</sup>C/I3C basic bus) and subsequently floats the PWR\_GOOD output signal. The timing parameter tPMIC\_PWR\_GOOD\_OUT applies here. This parameter represents the sum of the maximum soft-start time, the delay configured for each power-on sequence configuration register executed, plus an additional timing margin error of 5ms. The waveform indicates the soft-start time for each buck regulator output, as well as the delay time once the soft-start period concludes for each power-on sequence, from config0 to config2 registers.

It is important to note that if more than one regulator is enabled in a power-on sequence config register, and these regulators have different programmed soft-start times, the longest soft-start time will be used as the reference for the delay timer to initiate. However, each regulator will still adhere to its distinct soft-start time for powering on the buck regulator.

In <u>Figure 9</u>, three power-on sequence config registers (config0 to config2) are used, and only one buck regulator is enabled in each of these registers.

Figure 9. Power On Timing for Power Supply Rails

Copyright © 2024 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation

### 15.3 Secure Mode and Programmable Mode of Operation

Before issuing a VR Enable command (using the VR\_EN pin or via the I<sup>2</sup>C/I3C basic bus), the host must appropriately configure Register 0x2F [2] as required. Once the VR Enable command is received, the RTQ5132 offers two modes of operation:

- 1. Programmable Mode: Regardless of when the VR Enable command is issued, the RTQ5132 permits the host to modify any register in the host region, and the PMIC responds accordingly.

- 2. Secure Mode: Following the issuing of the VR Enable command, the RTQ5132 prohibits modification to certain registers, including Register 0x15 to Register 0x2F, Register 0x32 [7,5:0] in the host region, and Register 0x40 to Register 0x6F in the DIMM vendor region. These registers are write-protected. To make any changes, the host must power cycle the RTQ5132, defined as completely removing the VIN Bulk input supply to the RTQ5132. This definition is consistent throughout the entire specification.

Note that Secure Mode becomes relevant only after the VR Enable command has been registered. By default, Register 0x2F [2] is set to '0' when the RTQ5132 is first powered up. Before the VR Enable command is issued, the RTQ5132 permits modifications to any registers in the host region.

#### 15.4 Power Down Output Regulators

The RTQ5132 powers down its output regulators based on its mode of operation, regardless of whether the output regulators are activated using the VR\_EN pin or a VR Enable command on the I2C/I3C basic bus. The powerdown is described in the following sub-sections:.

### Programmable Mode Operation; 0x1A[4] = '0'

The RTQ5132 allows the user to power down any or all output regulators using any of the three methods below:

- 1. The VR Disable command (setting Register 0x32[7] to '0' or transitioning the VR\_EN pin to low) triggers the RTQ5132 to execute the power-off sequence from config0 (Register 0x58) to config2 (Register 0x5A) in order to maintain the appropriate voltage relationships as configured in the registers. The RTQ5132 then controls the PWR\_GOOD signal as follows in points (1) and (2):

- (1) If the VR Disable command is initiated by a pin transition (the VR EN pin transitioning to Low), the RTQ5132 asserts the PWR GOOD signal to Low. The host can re-enable the RTQ5132's output regulators by transitioning the VR EN pin to High. After this transition, the RTQ5132 will execute the power-on sequence from config0 to config2 registers and will float the PWR\_GOOD signal once the tPMIC\_PWR\_GOOD\_OUT timing parameter is met.

- (2) If the VR Disable command is issued on an I<sup>2</sup>C/I3C bus (setting Register 0x32[7] to '0'), the RTQ5132 keeps the PWR GOOD signal floating. This indicates an intentional command from the host rather than a fault condition. The host can re-enable the RTQ5132's output regulators by issuing a VR EN command on the I<sup>2</sup>C/I3C bus (setting Register 0x32[7] to '1'). The RTQ5132 then executes the power-on sequence from config0 to config2 registers, continuing to float the PWR GOOD signal until the tPMIC PWR GOOD OUT time is satisfied. At that point, the RTQ5132 assumes normal control of the PWR\_GOOD signal.

Simultaneous use of the VR\_EN pin and the I<sup>2</sup>C/I3C bus command to control the RTQ5132 is not permitted. If the VR\_EN pin transitions to Low first, the PWR\_GOOD signal responds as described in point (1) and remains low even if a subsequent I<sup>2</sup>C/I3C bus command is issued, as mentioned in point (2).

2. Configuring one or more bits in Register 0x2F[6,4:3] to '0' allows the user to determine a specific sequence. The RTQ5132 will not automatically execute the power-off sequence from config0 (Register 0x58) to config2 (Register 0x5A). It maintains the PWR\_GOOD signal in a floating state because this represents an intentional

command by the user rather than a fault condition. Note that the user can re-enable any disabled output regulators by setting one or more bits in Register 0x2F[6,4:3] to '1', following any specific sequence they prefer. During this process, the PWR\_GOOD signal remains floating.

3. If Register 0x32[5] = '1', driving PWR\_GOOD input low. The RTQ5132 executes power-off sequence from config0 (Register 0x58) to config2 (Register 0x5A) to preserve the appropriate voltage relationship as configured in the registers and drives the PWR\_GOOD signal low. The RTQ5132 preserves all register contents, including the MTP error log registers. If the user re-enables RTQ5132's output regulators by issuing the VR\_EN command on the I<sup>2</sup>C/I3C basic bus (setting Register 0x32[7] = '1'), the RTQ5132 executes the power-on sequence from config0 to config2 registers and floats the PWR\_GOOD output signal after the tPMIC\_PWR\_GOOD\_OUT timing parameter is satisfied. The RTQ5132 does not require a power cycle.

The RTQ5132, can generate an internal VR Disable command at any time due to one or more events listed in <u>Table 3</u>. The RTQ5132 executes the power-off sequence from config0 (Register 0x58) to config2 (Register 0x5A) to preserve the appropriate voltage relationship as configured in the registers. The RTQ5132 asserts the PWR\_GOOD signal low. The user can re-enable RTQ5132's output regulators with a VR Enable command by either setting Register 0x32[7] ='1' or transitioning the VR\_EN pin to high. The RTQ5132 then turns on its output regulators and floats the PWR\_GOOD signal. The RTQ5132 does not require a power cycle.

### 15.4.2 Programmable Mode Operation; 0x1A[4] = '1'

The RTQ5132 allows the user to power down any or all output regulators by any of the three methods below:

- 1. The VR Disable command (Register 0x32[7] ='0' or VR\_EN pin transitions to low): The RTQ5132 executes the power-off sequence config0 (Register 0x58) to config2 (Register 0x5A) to preserve the appropriate voltage relationship as configured in the registers and enters the P1 state. The RTQ5132 controls the PWR\_GOOD signal as follows in (1) and (2):

- (1) If the VR Disable command comes with a pin (VR\_EN transitions to Low), the RTQ5132 asserts the PWR\_GOOD signal Low. The user can re-enable the RTQ5132's output regulators by transitioning the VR\_EN pin to High. The RTQ5132 exits the P1 state and executes the power-on sequence from config0 to config2 registers and floats the PWR\_GOOD signal after the tPMIC\_PWR\_GOOD\_OUT timing parameter is satisfied.

- (2) If the VR Disable command is issued via a I<sup>2</sup>C/I3C basic bus (Register 0x32[7] ='0'), the RTQ5132 keeps the PWR\_GOOD signal floating because this is an intentional command from the user and not a fault condition. The RTQ5132 exits from the P1 state with only the VR\_EN pin transition to High. The user can re-enable the RTQ5132's output regulators by transitioning the VR\_EN pin to High, and the RTQ5132 executes the power-on sequence from config0 to config2 registers. The RTQ5132 continues to float the PWR\_GOOD signal until the tPMIC\_PWR\_GOOD\_OUT timing parameter is satisfied, at which point the RTQ5132 assumes normal control of the PWR\_GOOD signal.

- (3) The simultaneous usage of the VR\_EN pin and I<sup>2</sup>C/I3C bus command to turn on/off the RTQ5132 is not allowed. If the VR\_EN pin transitions to Low first, the PWR\_GOOD signal follows as described in (1) and the PWR\_GOOD signal remains low even if there is a subsequent I<sup>2</sup>C/I3C bus command as described in (2).

- 2. Configure one or more bits in Register 0x2F [6, 4:3] to '0' in any specific sequence desired by the user. The RTQ5132 does not execute the power-off sequence from config0 (Register 0x58) to config2 (Register 0x5A) on its own. The RTQ5132 keeps the PWR\_GOOD signal floating because this is an intentional command from the host and not a fault condition. Note that the user can re-enable any of the disabled output regulators by configuring one or more bits in Register 0x2F[6, 4:3] to '1' in any specific sequence desired by the host. The RTQ5132 keeps the PWR\_GOOD signal floating.

Copyright © 2024 Richtek Technology Corporation. All rights reserved.

3. If Register 0x32[5] = '1', the PWR GOOD input is driven low. The RTQ5132 executes the power-off sequence from config0 (Register 0x58) to config2 (Register 0x5A) to preserve the appropriate voltage relationship as configured in the registers and drives PWR GOOD signal low. The RTQ5132 preserves all register contents, including the MTP error log registers. The RTQ5132 does not enter the P1 state. If the user re-enables the RTQ5132's output regulators by issuing the VR EN command on the  $I^2C/I3C$  Basic bus (Register 0x32[7] = '1'), the RTQ5132 executes power-on sequence from config0 to config2 registers and floats the PWR\_GOOD signal after the tPMIC PWR GOOD OUT timing parameter is satisfied. The RTQ5132 does not require a power cycle.

The RTQ5132 can generate an internal VR Disable command at any time due to one or more events listed in Table 3. The RTQ5132 executes the power-off sequence from config0 (Register 0x58) to config2 (Register 0x5A) to preserve the appropriate voltage relationship as configured in the registers. The RTQ5132 does not enter the P1 state. The RTQ5132 asserts the PWR\_GOOD signal low. The user can re-enable RTQ5132's output regulators with the VR Enable command by setting either Register 0x32[7] = '1' or transitioning the VR\_EN pin to high. The RTQ5132 turns on its output regulators and sets the PWR\_GOOD signal to float. The RTQ5132 does not require a power cycle.

#### 15.4.3 Secure Mode Operation; R1A[4] = '0'

The RTQ5132 allows the user to power down any or all output regulators by either of the two methods below:

- 1. The VR Disable command with the VR EN pin transitions to low. The RTQ5132 asserts the PWR GOOD signal to Low. The RTQ5132 executes the power-off sequence from config0 (Register 0x58) to config2 (Register 0x5A) to preserve the appropriate voltage relationship as configured in the registers. The user can re-enable the RTQ5132's output regulators by transitioning the VR EN pin to High. The RTQ5132 executes the power-on sequence from config0 to config2 registers and floats the PWR\_GOOD signal after the tPMIC\_PWR\_GOOD\_OUT timing parameter is satisfied. The RTQ5132 does not require a power cycle. Note that the VR Disable or Enable command on a I<sup>2</sup>C/I3C basic bus (for example, Register 0x32[7] = '0' or '1') has no effect on the RTQ5132. Also, configuring one or more bits in Register 0x2F[6, 4:3] to '0' has no effect on the RTQ5132.

- 2. If Register 0x32[5] ='1', the PWR GOOD input is driven low. The RTQ5132 executes the power-off sequence from config0 (Register 0x58) to config2 (Register 0x5A) to preserve the appropriate voltage relationship as configured in the registers. It drives the PWR GOOD signal low and unlocks only Register 0x32[7]. The RTQ5132 preserves all register contents, including the MTP error log registers and keeps all write protect registers locked except for the Register 0x32[7]. When the user issues a VR Enable command by I<sup>2</sup>C/I3C basic bus, the RTQ5132 executes the power-on sequence from config0 to config2 registers, floats the PWR GOOD output signal after the tPMIC\_PWR\_GOOD\_OUT timing parameter is satisfied, and re-locks register Register 0x32[7]. The RTQ5132 does not require a power cycle to re-enable RTQ5132's output regulators.

The RTQ5132 can generate an internal VR Disable command at any time due to one or more events listed in Table 3. The RTQ5132 executes the power-off sequence from config0 (Register 0x58) to config2 (Register 0x5A) to preserve the appropriate voltage relationship as configured in the registers. The RTQ5132 asserts the PWR\_GOOD signal low. The RTQ5132 requires a power cycle. The VR Enable command, with Register 0x32[7] = '1', or the VR EN pin transitioning to high, has no effect on the RTQ5132, and the RTQ5132 keeps its PWR GOOD signal low.

### 15.4.4 Secure Mode Operation; 0x1A[4] = '1'

The RTQ5132 allows the user to power down any or all output regulators by either of the two methods below:

- 1. The VR Disable command with the VR\_EN pin transitions to low. The RTQ5132 asserts the PWR\_GOOD signal Low. The RTQ5132 executes the power-off sequence from config0 (Register 0x58) to config2 (Register 0x5A) to preserve the appropriate voltage relationship as configured in the registers and enters the P1 state. The user can re-enable the RTQ5132's output regulators by transitioning the VR\_EN pin to High. The RTQ5132 exits the P1 state and executes the power-on sequence from config0 to config2 registers, and floats the PWR\_GOOD signal after the tPMIC\_PWR\_GOOD\_OUT timing parameter is satisfied. Note that the VR Disable or Enable command on an I<sup>2</sup>C/I3C basic bus (for example, Register 0x32[7] = '0' or '1') has no effect on the RTQ5132. Also, configuring one or more bits in Register0x2F[6, 4:3] to '0' has no effect on the RTQ5132.

- 2. If Register 0x32[5] ='1', the PWR\_GOOD input is driven low. The RTQ5132 executes the power-off sequence from config0 (Register 0x58) to config2 (Register 0x5A) to preserve the appropriate voltage relationship as configured in the registers. It drives the PWR\_GOOD signal low and unlocks only Register 0x32[7]. The RTQ5132 preserves all register contents, including the MTP error log registers and keeps all write protect registers locked except for the Register 0x32[7]. When the user issues the VR Enable command by the I<sup>2</sup>C/I3C basic bus, the RTQ5132 executes the power-on sequence from config0 to config2 registers, floats the PWR\_GOOD output signal after the tPMIC\_PWR\_GOOD\_OUT timing parameter is satisfied, and re-locks Register 0x32[7]. The RTQ5132 does not require a power cycle to re-enable RTQ5132's output regulators.

The RTQ5132 can generate an internal VR Disable command at any time due to one or more events listed in <u>Table 3</u>. The RTQ5132 executes the power-off sequence from config0 (Register 0x58) to config2 (Register 0x5A) to preserve the appropriate voltage relationship as configured in the registers. The RTQ5132 does not enter the P1 state. The RTQ5132 asserts the PWR\_GOOD signal low. The RTQ5132 requires a power cycle. The VR Enable command, with either Register 0x32[7] = '1', or the VR\_EN

pin transitioning to high, has no effect on the RTQ5132 and the RTQ5132 keeps its PWR GOOD signal low.

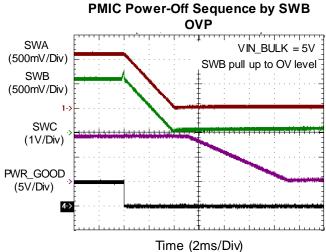

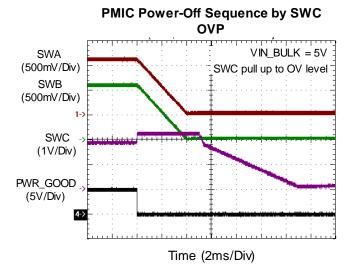

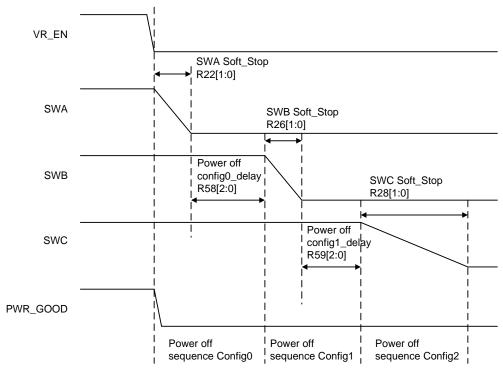

#### 15.5 PMIC Output Rail Off Timing

Figure 10 shows the timing relationship once the RTQ5132 registers receive a VR Disable command internally due to a fault condition, as listed in Events Interrupt Summary. The waveform shows soft-stop time and delay time for each buck regulator output once the soft-stop time expires from each power-off sequence config0 to power-off sequence config2 registers. Note that if more than one regulator is disabled in a power-off sequence config register and these regulators have different programmed soft-stop times, then the larger soft-stop time value is used as a reference for the delay timer to start. Each regulator will still follow different soft-stop time to turn off the buck regulator.

The specific example in <u>Figure 12</u> uses only three power-off sequence config0 to config2 registers and only one buck regulator is disabled in each of the power-off sequence config0, config1, and config2 registers.

Figure 10. PMIC Power Off Timing Due to Internal Fault Condition

### 15.6 GSI n Signal

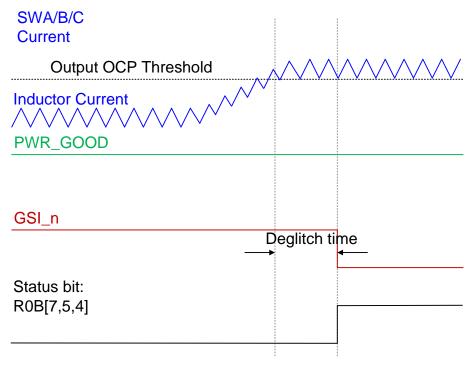

The RTQ5132 features a general-purpose interrupt, GSI\_n, for signaling any event to the user. The GSI\_n is an open-drain output pin that needs an external pull-up resistor (~10kΩ) to 3.3V or 1.8V.

The interrupts are active Low "latched" signals. When an interrupt event occurs in the RTQ5132, a low level is output on the corresponding interrupt pin.

The interrupt pin is held low until both of the following requirements are met:

- 1. The condition causing the interrupt (or any other condition that has occurred since) no longer persists.

- 2. The register is cleared through an I<sup>2</sup>C or I3C write to the clear bit.

All warning status bits are latched to '1' based on their condition occurring. The latch remains at '1' until the corresponding clear bit is written with a '1'. If an exception bit is cleared, but the condition continues to persist, a new interrupt will be generated as if it is a new condition.

When the GSI\_n signal is asserted, the RTQ5132 continues to operate normally.

The user can guery the appropriate status registers to determine and isolate the cause of the GSI\_n signal assertion.

2024

Table 1. Summary of GSI\_n Assertion Events

| No | Event Description                                             |

|----|---------------------------------------------------------------|

| 1  | Input (VIN_BULK) Power-Good status.                           |

| 2  | Input (VIN_BULK) Overvoltage protection.                      |

| 3  | Output (SW[A:C] or VLDO_1.8V, VLDO_1.0V) Power-Good status.   |

| 4  | Output (SW[A:C]) Overvoltage protection.                      |

| 5  | Output (SW[A:C]) Undervoltage-Lockout protection.             |

| 6  | LDO Output or VIN_BULK Input Undervoltage-Lockout protection. |

| 7  | Output (SW[A:C]) Current Limiter Warning event.               |

| 8  | Output (SW[A:C]) High Current Consumption Warning event.      |

| 9  | PMIC High Temperature Warning status.                         |

| 10 | PMIC Critical Temperature protection.                         |

| 11 | PEC Error.                                                    |

| 12 | Parity Error.                                                 |

#### 15.7 Power State Definition

This section provides detailed definitions for Quiescent Power State and Idle Power State.

Table 2 describes the definition for each power state, including the conditions and characteristics of each state, to help understand how to efficiently transition between different power modes.

#### 15.7.1 Quiescent Power State

- VIN\_Bulk nominal = 5.0V.

- All circuits including the RTQ5132 switch output and LDO output regulators are off.

- The VR\_EN signal is at a static low or high level.

- The I<sup>2</sup>C or I3C basic interface access is not allowed and is pulled high.

- The PID signal is at a static low or high level.

This state is only applicable if Register 0x1A[4] = '1'. This state is labeled as P1 state below.

#### 15.7.2 **Idle Power State**

- VIN Bulk nominal = 5.0V.

- All circuits including the RTQ5132 switch output and LDO output regulators are on with 0A load.

- The VR\_EN signal is at a static low or high level.

- The I<sup>2</sup>C or I3C basic interface access is allowed but the bus is pulled high.

- The PID signal is at static low or high level.

This state is only applicable if Register 0x1A[4] = '0'. This state is the same as the P3 state, but the load on all switch output regulators and LDO output regulators is 0A.

**Table 2. Power State Definition**