# **RTQ2516**

# 2A, Low Input Voltage, Ultra-Low Dropout LDO Regulator with Enable

### 1 General Description

The RTQ2516 is a high performance positive voltage regulator designed for use in applications requiring ultra- low input voltage and ultra-low dropout voltage at up to 2 amperes. It operates with an input voltage as low as 1.4V, with output voltage programmable as low as 0.5V. The RTQ2516 features ultra low dropout, ideal for applications where output voltage is very close to input voltage. Additionally, the RTQ2516 has an enable pin to further reduce power dissipation while shutdown. The RTQ2516 provides excellent regulation over variations in line, load and temperature. The RTQ2516 is available in the SOP-8 (Exposed Pad) package. The output voltage can be set by an external divider depending on how the FB pin is configured. The recommended junction temperature range is -40°C to 125°C.

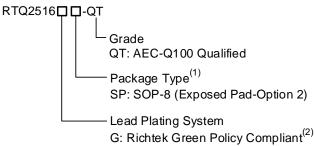

### 2 Ordering Information

#### Note 1

- Marked with <sup>(1)</sup> indicated: Compatible with the current requirements of IPC/JEDEC J-STD-020.

- Marked with <sup>(2)</sup> indicated: Richtek products are Richtek Green Policy compliant.

### 3 Features

- AEC-Q100 Grade 2 Qualified

- Input Voltage as Low as 1.4V

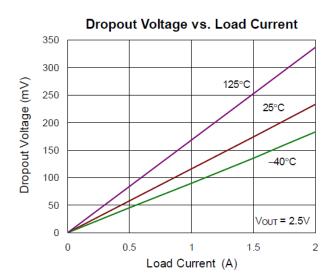

- Ultra-Low Dropout Voltage 400mV at 2A

- Overcurrent Protection

- Over-Temperature Protection

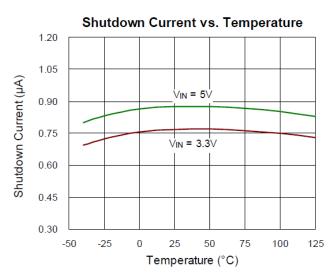

- 1µA Input Current in Shutdown Mode

- Enable Control

### 4 Applications

- Telecom/Networking Cards

- Motherboards/Peripheral Cards

- Industrial Applications

- Wireless Infrastructure

- Set Top Box

- Medical Equipment

- Notebook Computers

- Battery Powered Systems

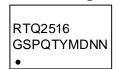

### 5 Marking Information

RTQ2516GSPQT: Product Code YMDNN: Date Code

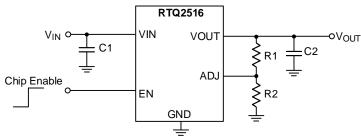

# 6 Simplified Application Circuit

Copyright © 2024 Richtek Technology Corporation. All rights reserved.

RICHTEK

is a registered trademark of Richtek Technology Corporation.

# **Table of Contents**

| 1  | General Description1               |    | 17.2   | Output Undervoltage Protection (UVP) |    |

|----|------------------------------------|----|--------|--------------------------------------|----|

| 2  | Ordering Information1              |    |        | and Over- Current Fold-Back          | 9  |

| 3  | Features1                          |    | 17.3   | Soft-Start                           | 9  |

| 4  | Applications 1                     |    | 17.4   | Over-Temperature Protection (OTP)    | 9  |

| 5  | Marking Information1               | 18 | Appli  | cation Information                   | 10 |

| 6  | Simplified Application Circuit1    |    | 18.1   | Output Voltage Setting               | 10 |

| 7  | Pin Configuration3                 |    | 18.2   | Chip Enable Operation                | 10 |

| 8  | Functional Pin Description3        |    | 18.3   | Current Limit                        |    |

| 9  | Functional Block Diagram3          |    | 18.4   | CIN and COUT Selection               |    |

| 10 | Absolute Maximum Ratings4          |    | 18.5   | Thermal Considerations               | 10 |

| 11 | ESD Ratings4                       | 19 | Outlir | ne Dimension                         | 12 |

| 12 | Recommended Operating Conditions4  | 20 | Footp  | orint Information                    | 13 |

| 13 | Thermal Information4               | 21 | Packi  | ng Information                       |    |

| 14 | Electrical Characteristics5        |    | 21.1   | Tape and Reel Data                   |    |

| 15 | Typical Application Circuit6       |    | 21.2   | Tape and Reel Packing                | 15 |

| 16 | Typical Operating Characteristics7 |    | 21.3   | Packing Material Anti-ESD Property   | 16 |

| 17 | Operation9                         | 22 | Datas  | heet Revision History                | 17 |

|    | 17.1 Reverse Current Protection 9  |    |        |                                      |    |

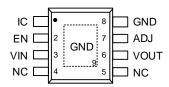

# 7 Pin Configuration

(TOP VIEW)

SOP-8 (Exposed Pad)

# **8 Functional Pin Description**

| Pin No.               | Pin Name | Pin Function                                                                                                                                                                                                                                                                                                                                |

|-----------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                     | IC       | Internal connection. Keep this pin floating for normal operation.                                                                                                                                                                                                                                                                           |

| 4, 5                  | NC       | No internal connection.                                                                                                                                                                                                                                                                                                                     |

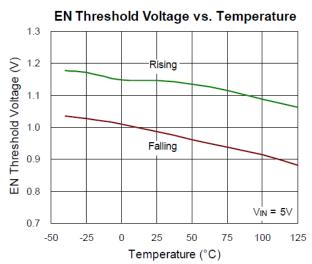

| 2                     | EN       | Chip enable (Active-High). Pulling this pin below 0.4V to turn the regulator off. The device will be enabled if this pin is left open. Connect to VIN for controlling by VIN.                                                                                                                                                               |

| 3                     | VIN      | Power input. For regulation at full load, the input to this pin must be between (Vout + 0.5V) and 6V. Minimum input voltage is 1.4V. A large bulk capacitance should be placed closely to this pin to ensure that the input supply does not sag below 1.4V. A minimum of $10\mu F$ ceramic capacitor should be placed directly at this pin. |

| 6                     | VOUT     | LDO output pin. Connect a ceramic capacitor with an capacitance of at least $10\mu F$ as close as possible from this pin to GND to minimize the input impedance.                                                                                                                                                                            |

| 7                     | ADJ      | Feedback voltage input. This pin is used to set the output voltage via an external resistive voltage divider. The feedback reference voltage is 0.5V (typical). Place the resistive voltage divider as close to the FB pin as possible. Do not leave this pin floating.                                                                     |

| 8,<br>9 (Exposed pad) | GND      | Ground. This pin must be soldered to a large PCB copper area for maximum power dissipation.                                                                                                                                                                                                                                                 |

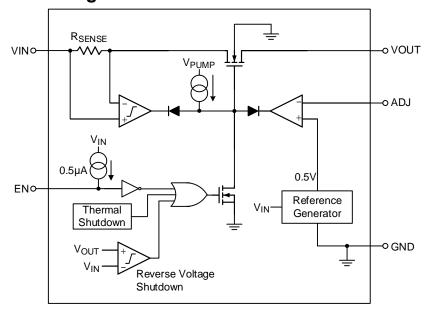

# 9 Functional Block Diagram

Copyright © 2024 Richtek Technology Corporation. All rights reserved.

RICHTEK is a registered tr

is a registered trademark of Richtek Technology Corporation.

### 10 Absolute Maximum Ratings

#### (Note 2)

- Supply Voltage, VIN------ -0.3V to 7V • Other Pins ------ -0.3V to 7V • Lead Temperature (Soldering, 10 sec.) ------ 260°C • Junction Temperature ------ 150°C

- Note 2. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

### 11 ESD Ratings

#### (Note 3)

- ESD Susceptibility

Note 3. Devices are ESD sensitive. Handling precautions are recommended.

# 12 Recommended Operating Conditions

### (Note 4)

- Supply Input Voltage, VIN ------ 1.4V to 6V • Junction Temperature Range----- --- -40°C to 125°C

- Note 4. Recommended operating conditions indicate conditions for which the device is intended to be functional, but do not ensure specific performance limits. For ensured specifications, see the Electrical Characteristics table.

### 13 Thermal Information

### (Note 5 and Note 6)

|                     | Thermal Parameter                                       | SOP-8 (Exposed Pad) | Unit |

|---------------------|---------------------------------------------------------|---------------------|------|

| θЈА                 | Junction-to-ambient thermal resistance (JEDEC standard) | 40.1                | °C/W |

| $\theta$ JC(Top)    | Junction-to-case (top) thermal resistance               | 63                  | °C/W |

| $\theta$ JC(Bottom) | Junction-to-case (bottom) thermal resistance            | 4.5                 | °C/W |

| θJA(EVB)            | Junction-to-ambient thermal resistance (specific EVB)   | 51.2                | °C/W |

| ΨJC(Top)            | Junction-to-top characterization parameter              | 10.9                | °C/W |

| ΨЈВ                 | Junction-to-board characterization parameter            | 32                  | °C/W |

- Note 5. For more information about thermal parameter, see the Application and Definition of Thermal Resistances report,

- Note 6. θJA(EVB), ΨJC(TOP), and ΨJB are measured on a high effective-thermal-conductivity two-layer test board which is in size of 70mm x 50mm; furthermore, all layers with 1 oz. Cu. Thermal resistance/parameter values may vary depending on the PCB material, layout, and test environmental conditions.

# 14 Electrical Characteristics

( $V_{IN}$  = 1.4V to 6V,  $I_{OUT}$  = 10 $\mu A$  to 2A,  $V_{ADJ}$  =  $V_{OUT}$ ,  $-40^{\circ}C \le T_A \le 105^{\circ}C$ , unless otherwise specified)

| Parameter                          | Symbol    | Test Conditions                                      | Min    | Тур | Max    | Unit     |  |  |

|------------------------------------|-----------|------------------------------------------------------|--------|-----|--------|----------|--|--|

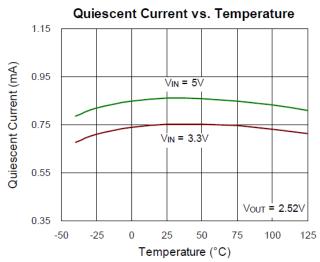

| Quiescent Current                  | IQ        | VIN = 3.3V, IOUT = 0A                                |        | 0.7 | 1.5    | mA       |  |  |

| Shutdown Current                   | ISHDN     | VIN = 6V, VEN = 0V                                   |        | 1.5 | 10     | μΑ       |  |  |

| Line Regulation                    | VLINE_REG | IOUT = 10mA                                          |        | 0.2 | 0.4    | %/V      |  |  |

| Load Regulation                    | VLOAD_REG | IOUT = 10mA to 2A                                    |        | 0.5 | 1.5    | %        |  |  |

|                                    |           | I <sub>OUT</sub> = 1A, V <sub>IN</sub> ≥ 1.6V        |        | 120 | 200    |          |  |  |

|                                    |           | IOUT = 1A, 1.4V < VIN < 1.6V                         |        |     | 400    |          |  |  |

| Dropout Voltage                    | VDROP     | IOUT = 1.5A, VIN ≥ 1.6V                              |        | 180 | 300    | mV       |  |  |

| Dropout Voltage                    | VDROP     | IOUT = 1.5A, 1.4V < VIN < 1.6V                       |        |     | 500    | IIIV     |  |  |

|                                    |           | IOUT = 2A, VIN ≥ 1.6V                                |        | 240 | 400    |          |  |  |

|                                    |           | I <sub>OUT</sub> = 2A, 1.4V < V <sub>IN</sub> < 1.6V |        |     | 600    |          |  |  |

| Current Limit                      | ILIM      | V <sub>IN</sub> = 3.3V                               | 2.3    | 3   | 4.4    | Α        |  |  |

| Feedback                           |           |                                                      |        |     |        |          |  |  |

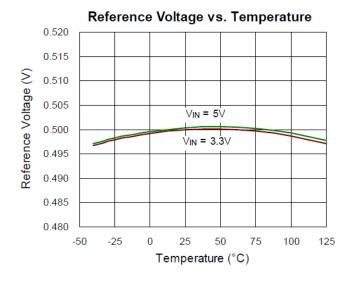

| ADJ Reference Voltage              | Voca      | VIN = 3.3V, VADJ = VOUT,<br>IOUT = 10mA, TA = 25°C   | 0.495  |     | 0.505  | <b>V</b> |  |  |

| ADJ Reference voltage              | VREF      | VIN = 3.3V, VADJ = VOUT,<br>IOUT = 10mA              | 0.4925 |     | 0.5075 | 1 V      |  |  |

| ADJ Pin Current                    | IADJ      | V <sub>ADJ</sub> = 0.5V                              |        | 20  | 200    | nA       |  |  |

| Enable                             |           |                                                      |        |     |        |          |  |  |

| EN Pin Current                     | IEN       | V <sub>EN</sub> = 0V, V <sub>IN</sub> = 6V           |        | 1   | 10     | μА       |  |  |

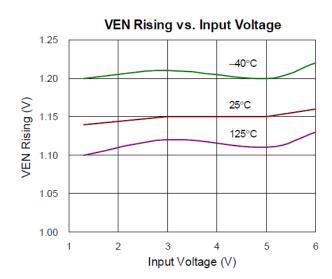

| EN Input Voltage Rising Threshold  | VEN_R     | VIN = 3.3V                                           | 1.6    |     |        | V        |  |  |

| EN Input Voltage Falling Threshold | VEN_F     | V <sub>IN</sub> = 3.3V                               |        |     | 0.4    | V        |  |  |

| Over-Temperature Prote             | ection    |                                                      |        |     |        |          |  |  |

| OTP Trip Level                     | Тотр      | Threshold                                            |        | 160 |        | °C       |  |  |

| Hysteresis                         | Totp_hys  | Hysteresis                                           |        | 30  |        | °C       |  |  |

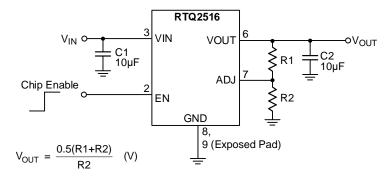

# 15 Typical Application Circuit

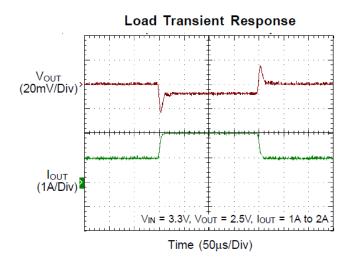

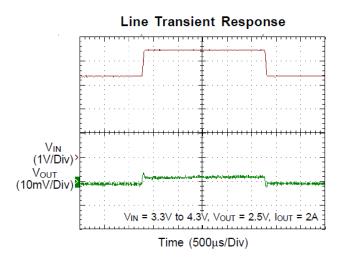

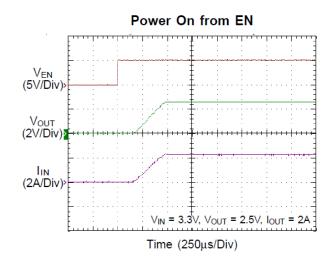

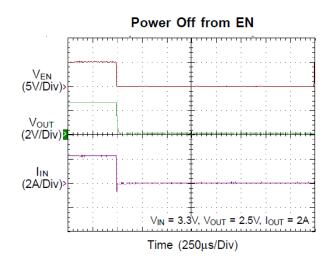

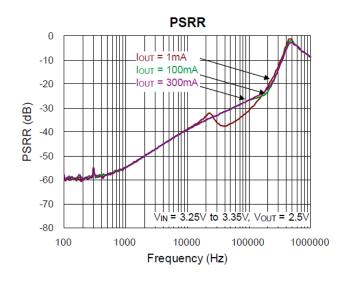

# 16 Typical Operating Characteristics

Copyright © 2024 Richtek Technology Corporation. All rights reserved.

www.richtek.com

### 17 Operation

The RTQ2516 is a low input voltage, low dropout LDO that can support an input voltage range from 1.4V to 6V and an output current of up to 2A. The RTQ2516 uses an internal charge pump to achieve low input voltage operation, and the internal compensation network is well designed to achieve fast transient response with good stability. In steady-state operation, the feedback voltage is regulated to the reference voltage by the internal regulator. When the feedback voltage signal is less than the reference, the on-resistance of the power MOSFET is decreased to increase the output current through the power MOSFET, and the feedback voltage will charge back to the reference. If the feedback voltage is greater than the reference, the power MOSFET current is decreased to make the output voltage discharge back to the reference by the loading current.

#### 17.1 Reverse Current Protection

The reverse current protection is guaranteed by the N-MOSFET with bulk capacitors connected to GND and the internal circuit. The reverse voltage detection circuit shuts the entire loop down if the output voltage is higher than the input voltage.

### 17.2 Output Undervoltage Protection (UVP) and Over- Current Fold-Back

When the feedback voltage is lower than 0.15V after the internal soft-start ends, the UVP is triggered. If the overcurrent condition is triggered during the UVP state, the OC limit current will be decreased to limit the output power and change into the re-soft-start state at the same time.

#### 17.3 Soft-Start

An internal current source charges an internal capacitor to build the soft-start ramp voltage. During the soft-start state, the output current will be limited to prevent inrush current.

#### 17.4 Over-Temperature Protection (OTP)

The RTQ2516 includes over-temperature protection (OTP) circuitry to prevent overheating. When the junction temperature exceeds the OTP threshold (TOTP), the device is disabled. It will automatically resume normal operation once the junction temperature decreases by the amount of OTP hysteresis (TOTP\_HYS). Additionally, continuous operation at or into thermal shutdown, or maintaining a junction temperature above 125°C may diminish the reliability of the RTQ2516.

Note that the over-temperature protection is designed to protect the device during temporary overload conditions. It serves as a secondary fail-safe mechanism and is activated when operating conditions exceed the absolute maximum range. It should not be used as a substitute for proper thermal design in normal operation. Continuously operating the device above the specified absolute maximum junction temperature compromise device reliability or result in permanent damage.

# 18 Application Information

(Note 7)

The RTQ2516 is a low voltage, low dropout linear regulator. It supports an input voltage range from 1.4V to 6V and an adjustable output voltage from 0.5V to (VIN – VDROP).

### 18.1 Output Voltage Setting

The RTQ2516 output voltage is adjustable from 0.5V to (VIN - VDROP) via the external resistive voltage divider. The voltage divider resistors can have values of up to  $800 \text{k}\Omega$  because of the very high impedance and low bias current of the sense comparator. The output voltage is set according to the following equation:

$$V_{OUT} = V_{REF} \times \left(1 + \frac{R1}{R2}\right)$$

where VREF is the reference voltage with a typical value of 0.5V.

### 18.2 Chip Enable Operation

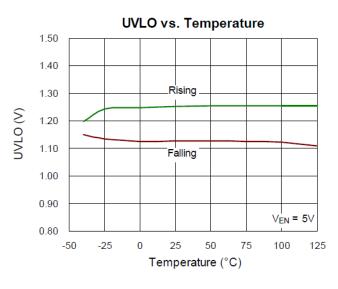

The RTQ2516 goes into sleep mode when the EN pin is in a logic low condition. In this condition, the pass transistor, error amplifier, and bandgap are all turned off, reducing the supply current to only  $10\mu$ A (max.). The EN pin can be directly tied to VIN to keep the part on.

#### 18.3 Current Limit

The RTQ2516 contains an independent current limit circuitry, which monitors and controls the pass transistor's gate voltage, limiting the output current to 3A (typ.).

### 18.4 CIN and COUT Selection

The RTQ2516 is designed specifically to work with low ESR ceramic output capacitors for space saving and performance considerations. Using a ceramic capacitor with a capacitance range from  $10\mu\text{F}$  to  $47\mu\text{F}$  on the output ensures stability. Input capacitance is selected to minimize transient input droop during load current steps. For general applications, an input capacitor with a value of  $10\mu\text{F}$  is recommended to minimize input impedance and provide the desired effect without affecting stability.

#### 18.5 Thermal Considerations

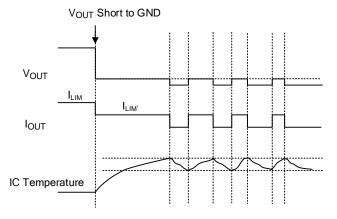

Thermal protection limits power dissipation in the RTQ2516. When the operating junction temperature exceeds 160°C, the OTP circuit starts the thermal shutdown function and turns the pass element off. The pass element turns on again after the junction temperature cools by 30°C. The RTQ2516 output voltage will be close to zero when an output short circuit occurs, as shown in <a href="Figure 1">Figure 1</a>. This can reduce the IC temperature and provide maximum safety to end users when an output short circuit occurs.

Figure 1. Short Circuit Protection when Output Short Circuit Occurs

The junction temperature should never exceed the absolute maximum junction temperature  $T_{J(MAX)}$ , listed under Absolute Maximum Ratings, to avoid permanent damage to the device. The maximum allowable power dissipation depends on the thermal resistance of the IC package, the PCB layout, the rate of surrounding airflow, and the difference between the junction and ambient temperatures. The maximum power dissipation can be calculated using the following formula:

$PD(MAX) = (TJ(MAX) - TA) / \theta JA$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction-to-ambient thermal resistance.

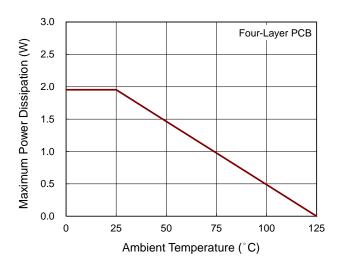

For continuous operation, the maximum operating junction temperature indicated under Recommended Operating Conditions is 125°C. The junction-to-ambient thermal resistance,  $\theta_{JA(EVB)}$ , is highly package dependent. For a SOP-8 package, the thermal resistance,  $\theta_{JA(EVB)}$ , is 51.2°C/W on a standard JEDEC 51-7 high effective-thermal-conductivity four-layer test board. The maximum power dissipation at TA = 25°C can be calculated as below:

$PD(MAX) = (125^{\circ}C - 25^{\circ}C) / (51.2^{\circ}C/W) = 1.95W$  for a SOP-8 package.

The maximum power dissipation depends on the operating ambient temperature for the fixed  $T_{J(MAX)}$  and the thermal resistance,  $\theta_{JA(EVB)}$ . The derating curves in <u>Figure 2</u> allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 2. Derating Curve of Maximum

**Note 7.** The information provided in this section is for reference only. The customer is solely responsible for the designing, validating, and testing your product incorporating Richtek's product and ensure such product meets applicable standards and any safety, security, or other requirements.

RICHTEK is a registered trademark of Richtek Technology Corporation.

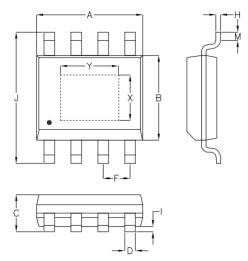

# 19 Outline Dimension

| O la     | -1  | Dimens | sions In | Dimension | s In Inches |  |

|----------|-----|--------|----------|-----------|-------------|--|

| Symb     | 101 | Min    | Max      | Min       | Max         |  |

| А        |     | 4.801  | 5.004    | 0.189     | 0.197       |  |

| В        |     | 3.810  | 4.000    | 0.150     | 0.157       |  |

| С        |     | 1.346  | 1.753    | 0.053     | 0.069       |  |

| D        |     | 0.330  | 0.510    | 0.013     | 0.020       |  |

| F        |     | 1.194  | 1.346    | 0.047     | 0.053       |  |

| Н        |     | 0.170  | 0.254    | 0.007     | 0.010       |  |

| I        |     | 0.000  | 0.152    | 0.000     | 0.006       |  |

| J        |     | 5.791  | 6.200    | 0.228     | 0.244       |  |

| М        |     | 0.406  | 1.270    | 0.016     | 0.050       |  |

| Ontion   | Χ   | 2.100  | 2.500    | 0.083     | 0.098       |  |

| Option 2 | Υ   | 3.000  | 3.500    | 0.118     | 0.138       |  |

8-Lead SOP (Exposed Pad) Plastic Package

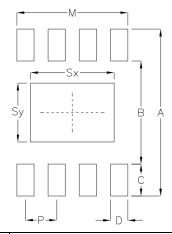

# 20 Footprint Information

| Pools  | ,000    | Number of Pin | Footprint Dimension (mm) |      |      |      |      |      |      |      | Tolerance |

|--------|---------|---------------|--------------------------|------|------|------|------|------|------|------|-----------|

| Pack   | age     | Number of Pin | Р                        | Α    | В    | С    | D    | Sx   | Sy   | М    |           |

| PSOP-8 | Option1 | Ω             | 1.27                     | 6 90 | 4.20 | 1.30 | 0.70 | 2.30 | 2.30 | 4.51 | ±0.10     |

| P30P-6 | Option2 | 0             | 1.27                     | 6.80 |      |      |      | 3.40 | 2.40 |      |           |

# 21 Packing Information

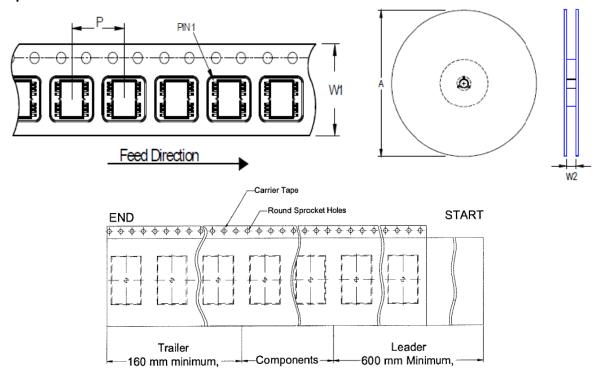

### 21.1 Tape and Reel Data

| Ded to Too   | Tape Size | Pocket Pitch | et Pitch Reel Size ( |      | Units    | Trailer | Leader | Reel Width (W2) |  |

|--------------|-----------|--------------|----------------------|------|----------|---------|--------|-----------------|--|

| Package Type | (W1) (mm) | (P) (mm)     | (mm)                 | (in) | per Reel | (mm)    | (mm)   | Min./Max. (mm)  |  |

| PSOP-8       | 12        | 8            | 330                  | 13   | 2,500    | 160     | 600    | 12.4/14.4       |  |

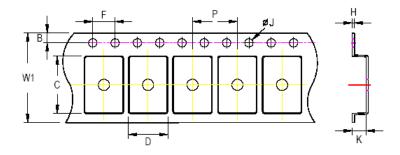

- C, D, and K are determined by component size. The clearance between the components and the cavity is as follows:

- For 12mm carrier tape: 0.5mm max.

| Tape Size | W1     | F     | )     | В      |        | F     |       | Ø٦    |       | Н     |

|-----------|--------|-------|-------|--------|--------|-------|-------|-------|-------|-------|

| Tapo Oizo | Max.   | Min.  | Max.  | Min.   | Max.   | Min.  | Max.  | Min.  | Max.  | Max.  |

| 12mm      | 12.3mm | 7.9mm | 8.1mm | 1.65mm | 1.85mm | 3.9mm | 4.1mm | 1.5mm | 1.6mm | 0.6mm |

# 21.2 Tape and Reel Packing

| Step | Photo/Description                      | Step | Photo/Description                 |

|------|----------------------------------------|------|-----------------------------------|

| 1    | Reel 13"                               | 4    | 1 reel per inner box <b>Box G</b> |

| 2    | HIC & Desiccant (2 Unit) inside        | 5    | 6 inner boxes per outer box       |

| 3    | Caution label is on backside of Al bag | 6    | Outer box Carton A                |

| Container | Reel |       | Вох   |       |       | Carton   |       |        |

|-----------|------|-------|-------|-------|-------|----------|-------|--------|

| Package   | Size | Units | Item  | Reels | Units | Item     | Boxes | Units  |

| PSOP-8    | 13"  | 2,500 | Box G | 1     | 2,500 | Carton A | 6     | 15,000 |

### 21.3 Packing Material Anti-ESD Property

| Surface<br>Resistance | Aluminum Bag                        | Reel                                | Cover tape                          | Carrier tape                        | Tube                                | Protection Band                     |

|-----------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|

| $\Omega$ /cm $^2$     | 10 <sup>4</sup> to 10 <sup>11</sup> |

### **Richtek Technology Corporation**

14F, No. 8, Tai Yuen 1st Street, Chupei City Hsinchu, Taiwan, R.O.C. Tel: (8863)5526789

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.

Copyright © 2024 Richtek Technology Corporation. All rights reserved.

22 Datasheet Revision History

| Version | Date      | Description | Item                                 |

|---------|-----------|-------------|--------------------------------------|

|         |           |             | General Description on P1            |

|         |           |             | Ordering Information on P1           |

|         |           |             | Functional Pin Description on P4     |

| 00      | 2024/6/17 | Modify      | Absolute Maximum Ratings on P5       |

|         |           |             | Thermal Information on P5            |

|         |           |             | Operation on P10                     |

|         |           |             | Packing Information on P15, P16, P17 |