### **Power Management Unit Total Power Solution for SSD**

### **General Description**

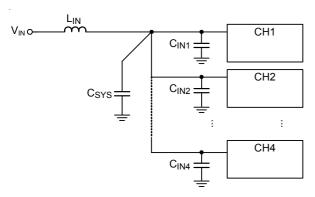

The RT5091A/B is a total power management solution for SSDs (Solid State Drive) with dedicated input supply voltages of 3.3V or 5V. The RT5091A/B incorporates three high-efficiency synchronous buck regulators and one LDO that deliver several output voltages from a single power source. This provides flexibility to support applications of different VIDs with a regulated power-on sequence.

The RT5091A/B can provide configurable output voltages to supply ASIC core, DDR, Flash I/O, and PHY. With a dedicated  $I^2C$  interface, it supports dynamic voltage scaling (DVS), and sleep mode for minimized standby power consumption.

### **Ordering Information**

RT5091A/B

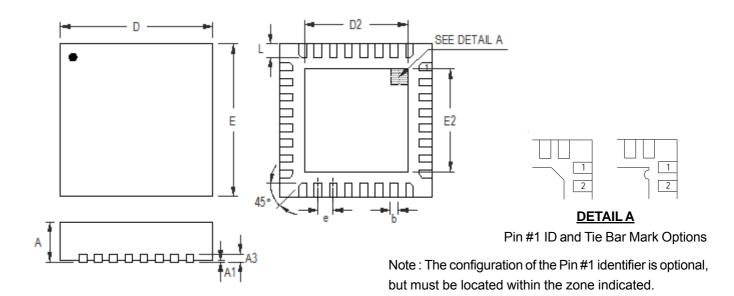

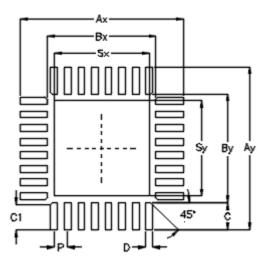

Package Type QW : WQFN-32L 4x4 (W-Type) Lead Plating System G : Green (Halogen Free and Pb Free) ——A : CH2/CH4 default voltage 1.35V/3.3V

B : CH2/CH4 default voltage 1.2V/1.8V

Note :

Richtek products are :

- ▶ RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- Suitable for use in SnPb or Pb-free soldering processes.

### Applications

Solid State Drives

### Features

- Input Supply Voltage Range : 2.8V to 5.5V

- Three High-Efficiency Configurable Low-Voltage Buck Converters at Default Switching Frequency of 2MHz

- CH1 for ASIC Core Power : Output Current : 4A

Output Voltages Programmable by REFIN Pin or 0.7V to 1.3V in 10mV/Step Via I<sup>2</sup>C

- CH2 for DDR Power :

- Output Current : 2A

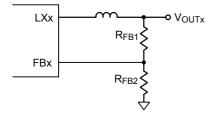

- Output Voltages Programmable by FB2 Pin

- CH3 for Flash I/O Power : Output Current : 2A

Output Voltages Programmable by FB3 Pin

- One LDO of Low Quiescent Current

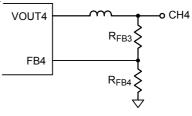

- ► LDO for Analog and PHY Power : Output Current : 300mA Output Voltages Programmable by FB4 Pin

- Gate Control for External N-MOSFET Against Inrush Current from Power Input

- Internal Soft-Start and Current Limit Protection for CH1 to CH3 and LDO

- STANDBY Pin for Sleep Mode Control

- Two Output Pins to Control External Regulators/ Switches

- One Input Pin to Sense External Regulators/ Switches Output Voltage

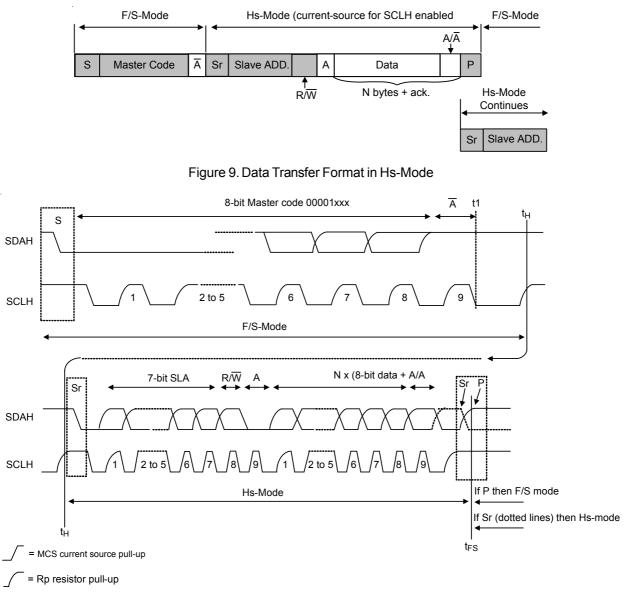

- High-Speed Mode I<sup>2</sup>C Interface for CH1 Output Voltage Programming

- PGOOD Indicator for VSYS, CH1 to CH3, and LDO Output Voltages Monitoring

- RST\_L Indicator for Reset Condition of VSYS

- Power-On Sequence Control During Start-up

- Over-Voltage Protection (OVP), Under-Voltage Protection (UVP), Under-Voltage Lockout (UVLO), and Thermal Shutdown Protection

- Small 32-Lead WQFN Package

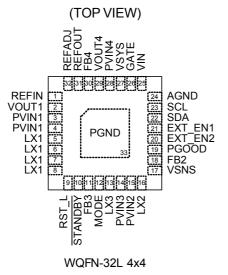

### **Pin Configuration**

### **Marking Information**

#### RT5091AGQW

63= : Product Code YMDNN : Date Code

#### RT5091BGQW

6S= : Product Code YMDNN : Date Code

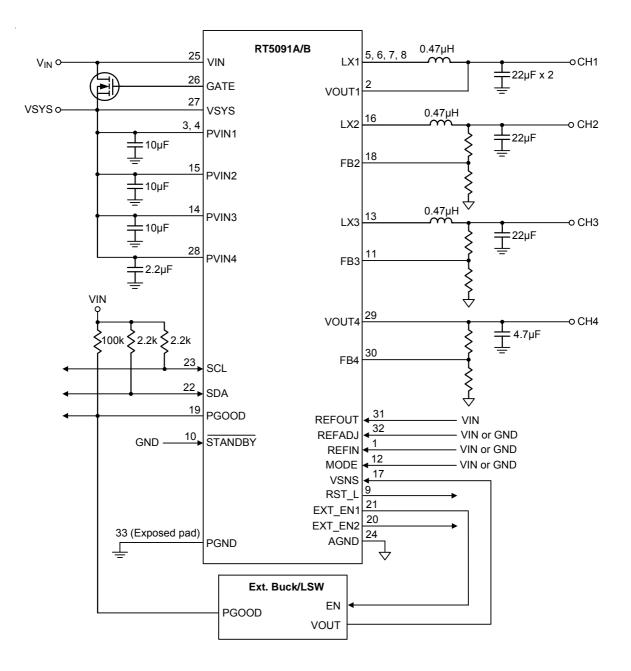

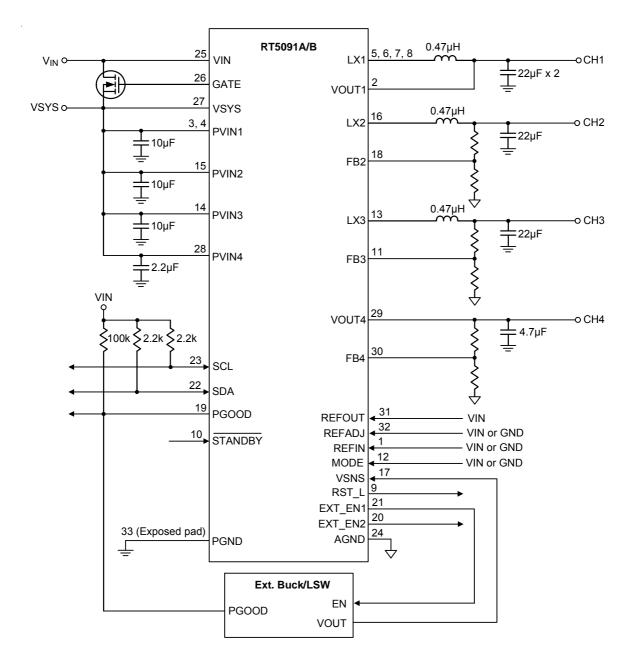

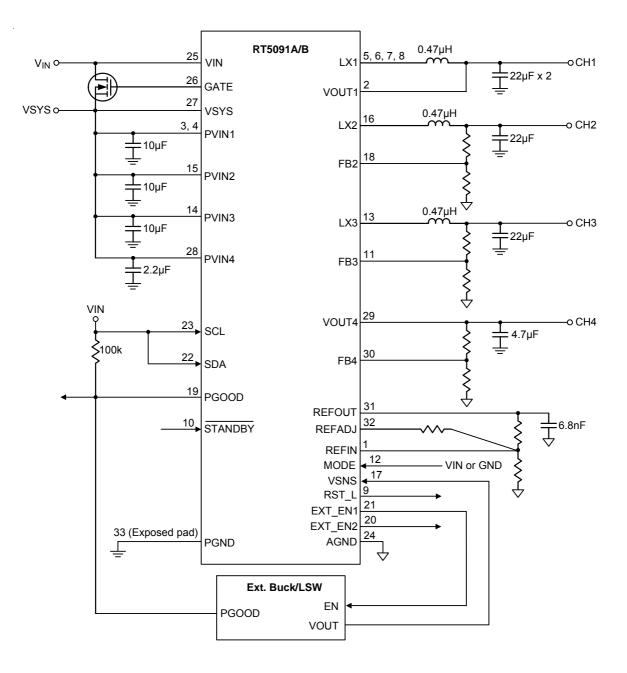

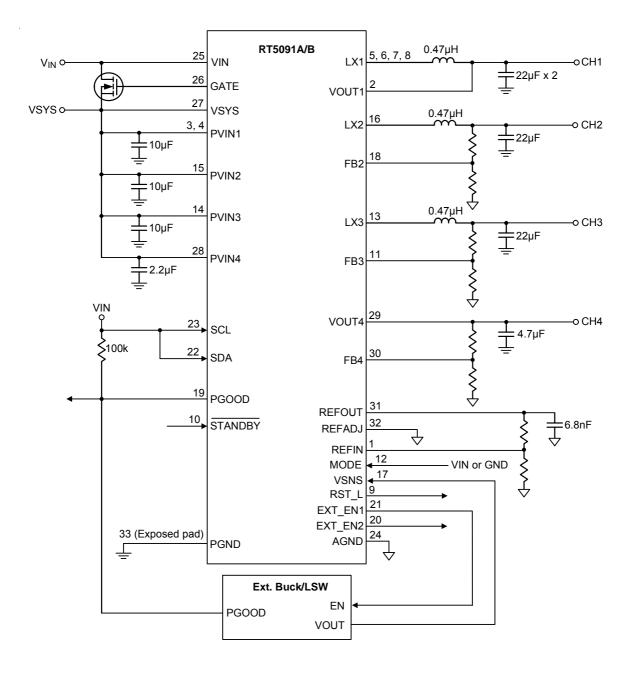

### **Typical Application Circuit**

#### Sleep Mode Operation by I<sup>2</sup>C & CH1 VOUT DVID by I<sup>2</sup>C

#### Sleep Mode Operation by $\overline{\text{STANDBY}}$ & CH1 VOUT DVID by I<sup>2</sup>C

#### Sleep Mode Operation by $\overline{\text{STANDBY}}$ & CH1 VOUT Adjustment at Sleep Mode & no I<sup>2</sup>C

#### Sleep Mode Operation by STANDBY & CH1 VOUT Adjustment via REFIN & no I<sup>2</sup>C

### **Functional Pin Description**

| Pin No.    | Pin Name | Pin Function                                                                                                                                                                                                                                                         |

|------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

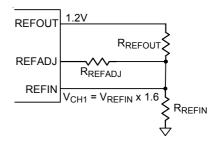

| 1          | REFIN    | CH1 external reference input. CH1 output voltage is equal to V <sub>REFIN</sub> x 1.6.                                                                                                                                                                               |

| 2          | VOUT1    | This pin is CH1 buck feedback input. Connect this pin to CH1 buck output. To disable this rail, connect this pin to VIN.                                                                                                                                             |

| 3, 4       | PVIN1    | CH1 buck converter power input.                                                                                                                                                                                                                                      |

| 5, 6, 7, 8 | LX1      | CH1 buck converter switch node.                                                                                                                                                                                                                                      |

| 9          | RST_L    | VSYS reset indication. Active-low open-drain output.                                                                                                                                                                                                                 |

| 10         | STANDBY  | Standby mode control pin. Refer to $\overline{\text{STANDBY}}$ control. Internal pull low by $1\mu A$ .                                                                                                                                                              |

| 11         | FB3      | This pin is CH3 buck feedback input. Connect this pin to a resistor divider to program CH3 output voltage, or directly to CH3 output node to have a default 1.8V for CH3 output voltage. To disable this rail, connect this pin to VIN.                              |

| 12         | MODE     | SATA 3.3V/5V select. MODE = Low, $V_{IN}$ = 3.3V; MODE = High, $V_{IN}$ = 5V. Internal pull low by 1µA.                                                                                                                                                              |

| 13         | LX3      | CH3 buck converter switch node.                                                                                                                                                                                                                                      |

| 14         | PVIN3    | CH3 buck converter power input.                                                                                                                                                                                                                                      |

| 15         | PVIN2    | CH2 buck converter power input.                                                                                                                                                                                                                                      |

| 16         | LX2      | CH2 buck converter switch node.                                                                                                                                                                                                                                      |

| 17         | VSNS     | External regulator output sense. If not used, tied to GND.                                                                                                                                                                                                           |

| 18         | FB2      | This pin is CH2 buck feedback input. Connect this pin to a resistor divider to program CH2 output voltage, or directly to CH2 output node to have a default 1.35V for RT5091A or 1.2V for RT5091B CH2 output voltage. To disable this rail, connect this pin to VIN. |

| 19         | PGOOD    | This is open drain type. It indicates all rails output and VSYS is ready or not.                                                                                                                                                                                     |

| 20         | EXT_EN2  | This pin is used to enable an external regulator/switch. Push-pull output. Should be floated if unused.                                                                                                                                                              |

| 21         | EXT_EN1  | This pin is used to enable an external regulator/switch. Push-pull output. Should be floated if unused.                                                                                                                                                              |

| 22         | SDA      | I <sup>2</sup> C interface data signal. Connect to VIN if not used.                                                                                                                                                                                                  |

| 23         | SCL      | I <sup>2</sup> C interface clock signal. Connect to VIN if not used.                                                                                                                                                                                                 |

| 24         | AGND     | Analog ground pin.                                                                                                                                                                                                                                                   |

| 25         | VIN      | Power input.                                                                                                                                                                                                                                                         |

| 26         | GATE     | This pin is used to control external power MOSFET. It should be connected to VIN if unused.                                                                                                                                                                          |

| 27         | VSYS     | System power sense.                                                                                                                                                                                                                                                  |

| 28         | PVIN4    | LDO input.                                                                                                                                                                                                                                                           |

| 29         | VOUT4    | LDO output.                                                                                                                                                                                                                                                          |

| 30         | FB4      | This pin is LDO feedback input. Connect this pin to a resistor divider to program CH4 output voltage, or set this pin floated to have a default 3.3V for RT5091A or 1.8V for RT5091B CH4 output voltage. To disable this rail, connect this pin to VIN.              |

| Pin No.          | Pin Name | Pin Function                                                                                                                                                                                                            |  |  |  |

|------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 31               | REFOUT   | Reference voltage output. It provides 1% high accuracy reference 1.2V with 0.1mA source ability. Bypass to GND with a 6.8nF ceramic capacitor. Series resistors connected to this pin should be lower than $1M\Omega$ . |  |  |  |

| 32               | REFADJ   | Reference adjustment output. Refer to PWM-VID Dynamic Voltage Control. If this pin is not used, ties to GND.                                                                                                            |  |  |  |

| 33 (Exposed Pad) | PGND     | Power ground. The exposed pad must be soldered to a large PCB and connected to PGND for maximum thermal dissipation.                                                                                                    |  |  |  |

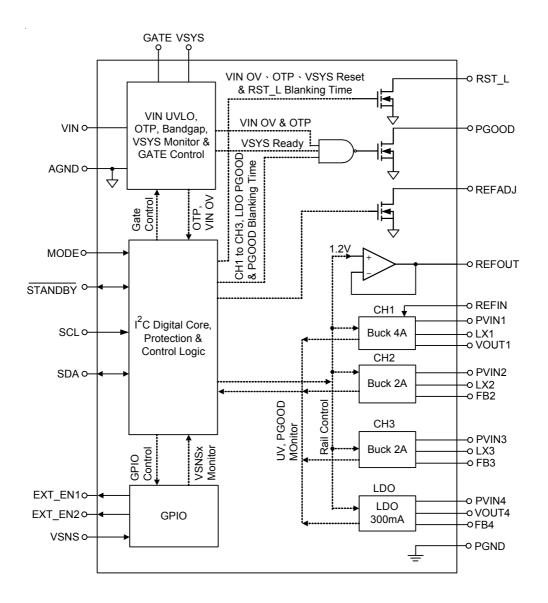

### **Functional Block Diagram**

### Operation

The RT5091A/B provides three high-efficiency synchronous buck regulators and one LDO for the power system of SSD.

#### **Buck Converter**

The RT5091A/B incorporates three high-efficiency synchronous switching buck converters that deliver programmable output voltages. They feature constant-on-time current mode for low output voltage, quick transient response, and low quiescent current. These buck converters also possess all standard protections.

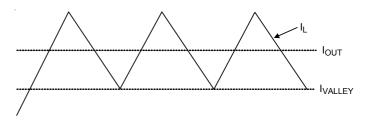

#### **Buck Over-Current Limiter (OCL)**

The buck converters provides current limiter for over-current protection through detecting low-side MOSFET current, which is known as the valley current limiter behavior. If the sensed inductor current is above the current limit threshold, then current limiter will start to constrain the valley of inductor current to the current limiter threshold until inductor current drops below the current limiter threshold.

#### **Buck Under-Voltage Protection (UVP)**

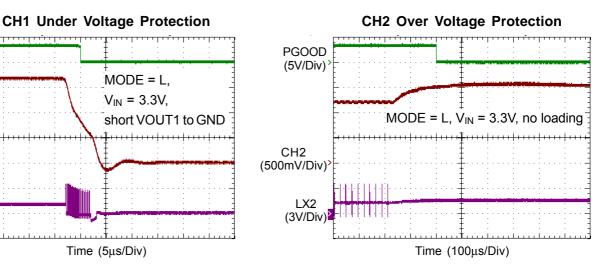

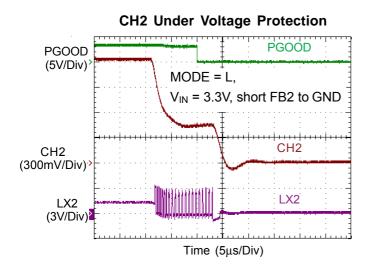

The output voltages are continuously monitored for undervoltage protection. If the output voltage falls below 62.5% of the reference voltage, under-voltage protection will be triggered and then the high-side and low-side MOSFET will be turned off. The UVP circuit will turn off all rails and latched. The only way to reset the latched behavior is restarting VIN power of the RT5091A/B.

#### **Buck Over-Voltage Protection (OVP)**

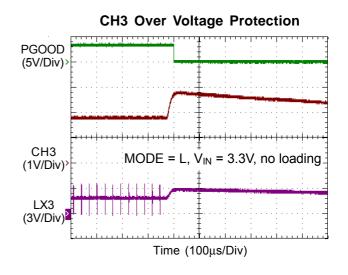

The output voltages are continuously monitored for overvoltage protection. If the output voltage exceeds 125% of the reference voltage, over-voltage protection will be triggered and then the high-side and low-side MOSFET will be turned off. The MOSFET drivers will keep in offstate until the over-voltage protection is released.

#### Linear Dropout Regulator (LDO)

The RT5091A/B includes one high performance linear dropout regulator. The LDO contains an independent current limit and under-voltage protection circuit to prevent

unexpected applications. When the path current is above the current limit threshold, the current limit circuit adjusts the gate voltage of power stage to limit the output current. Besides, if the output voltage is lower than 60% of reference voltage, the UVP circuit will turn off all rails and latched. The only way to reset the latched behavior is restarting VIN power of the RT5091A/B.

#### LDO Under-Voltage Protection (UVP)

The output voltages are continuously monitored for under voltage protection. If the output voltage falls below 60% of the reference voltage, under-voltage protection will be triggered and VOUT4 will be turned off. The UVP circuit will turn off all rails and latched. The only way to reset the latched behavior is restarting VIN power of the RT5091A/B.

#### **Over-Temperature Protection (OTP)**

If chip temperature is higher than  $150^{\circ}$ C, the OTP circuit will shut down all power rails. PMIC will reboot with powerup sequence after chip temperature cools down lower than  $125^{\circ}$ C.

#### GPIO

The RT5091A/B includes two external regulators/switches enable signals and one external regulator/switch output voltage sense.

#### MODE

MODE is an input pin to select the threshold voltage of VIN for POR. If VIN voltage is above the threshold voltage, PMIC will begin to start up with power-up sequence.

#### RST\_L

RST\_L is an output pin to inform the system that the VIN, VSYS, and VGATE are ready. If VSYS voltage is above the RST\_L rising threshold voltage, the RST\_L will be set to high. On the contrary, RST\_L will be set to low if VSYS voltage is lower than RST\_L falling threshold voltage.

### Absolute Maximum Ratings (Note 1)

| <ul> <li>Supply Input Voltage, VIN</li> <li>VSYS, PVIN1, PVIN2, PVIN3, PVIN4</li> <li>GATE</li> </ul> | –0.3V to 6V    |

|-------------------------------------------------------------------------------------------------------|----------------|

| • LX1, LX2, LX3 to GND                                                                                |                |

| <50ns                                                                                                 | –5V to 10V     |

| Other Pins                                                                                            | –0.3V to 6V    |

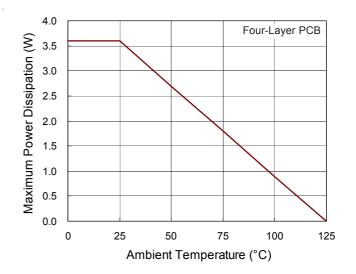

| • Power Dissipation, $P_D @ T_A = 25^{\circ}C$                                                        |                |

| WQFN-32L 4x4                                                                                          | 3.59W          |

| Package Thermal Resistance (Note 2)                                                                   |                |

| WQFN-32L 4x4, $\theta_{JA}$                                                                           | 27.8°C/W       |

| WQFN-32L 4x4, $\theta_{JC}$                                                                           |                |

| • Junction Temperature                                                                                | 150°C          |

| • Lead Temperature (Soldering, 10 sec.)                                                               | 260°C          |

| Storage Temperature Range                                                                             | –65°C to 150°C |

| • ESD Susceptibility (Note 3)                                                                         |                |

| HBM (Human Body Model)                                                                                | 2kV            |

### Recommended Operating Conditions (Note 4)

| Supply Input Voltage, VIN  | - 2.8V to 5.5V   |

|----------------------------|------------------|

| Other Pins                 | - 0V to 5.5V     |

| Junction Temperature Range | - –40°C to 125°C |

| Ambient Temperature Range  | - –40°C to 85°C  |

### **Electrical Characteristics**

(V<sub>IN</sub> = 3.3V,  $T_A$  = 25°C, unless otherwise specified)

| Parameter                        | Symbol           | Test Conditions                                                             | Min     | Тур   | Max     | Unit |

|----------------------------------|------------------|-----------------------------------------------------------------------------|---------|-------|---------|------|

| PMIC                             |                  |                                                                             |         |       |         |      |

| VIN Voltage Range                | Vvin             | MODE = low/high                                                             | 2.8/3.9 | 3.3/5 | 3.7/5.5 | V    |

| VIN Supply Current               | I <sub>VIN</sub> | All voltage rails, REFOUT buffer, VSNS GPIO & external MOSFET are disabled. |         | 20    |         | μA   |

| STANDBY Threshold =<br>High      | Vih              |                                                                             | 1.2     |       |         | V    |

| STANDBY Threshold =<br>Low       | VIL              |                                                                             |         |       | 0.4     | V    |

| VIN UVLO Threshold               |                  | Falling                                                                     | 2.1     | 2.2   | 2.3     | V    |

| VIN UVLO Threshold<br>Hysteresis |                  |                                                                             |         | 100   |         | mV   |

| Thermal Shutdown<br>Threshold    | T <sub>SD</sub>  | (Note 5)                                                                    |         | 150   |         | °C   |

| Thermal Shutdown<br>Hysteresis   | $\Delta T_{SD}$  | (Note 5)                                                                    |         | 25    |         | °C   |

## RT5091A/B

| Parameter                              | Symbol               | Test Conditions                                                                    | Min  | Тур | Max  | Unit  |

|----------------------------------------|----------------------|------------------------------------------------------------------------------------|------|-----|------|-------|

| VSYS Monitor                           |                      |                                                                                    |      |     |      |       |

| RESET Rising                           |                      | MODE = low                                                                         | 2.7  | 2.8 | 2.9  |       |

| Threshold                              | Vrstth_h             | MODE = high                                                                        | 3.7  | 3.8 | 3.9  | V     |

| RESET Falling<br>Threshold             | V <sub>RSTTH_L</sub> | If VSYS falls below V <sub>RSTTH_L</sub> , RST_L pull low.                         | 2.2  | 2.3 | 2.4  | V     |

| VSYS Ready Falling                     |                      | Program by PGOOD_VSYS_REG[2:1] via<br>I <sup>2</sup> C; MODE = low                 | 2.7  |     | 3    | v     |

| Threshold                              | VSYSRDY_L            | Program by PGOOD_VSYS_REG[2:1] via<br>I <sup>2</sup> C; MODE = high                | 3.8  |     | 4.1  |       |

| VSYS Ready<br>Threshold Step Size      |                      | Step size for I <sup>2</sup> C programming                                         |      | 100 |      | mV    |

| VSYS Ready Falling                     |                      | MODE = low; VSYS ready falling default threshold                                   | 2.6  | 2.7 | 2.8  | V     |

| Accuracy                               |                      | MODE = high; VSYS ready falling default threshold                                  | 3.65 | 3.8 | 3.95 | V     |

| VSYS Ready<br>Hysteresis               |                      |                                                                                    |      | 150 |      | mV    |

| External N-MOSFET S                    | witch                |                                                                                    |      |     |      |       |

| Quiescent Current                      |                      | External N-MOSFET are enabled                                                      |      | 30  |      | μA    |

| GATE Control Current                   |                      | Source current from GATE                                                           |      | 875 |      | nA    |

| VIN OVP                                |                      | MODE = low                                                                         | 3.8  |     | 4    | - v   |

| VINOVE                                 |                      | MODE = high                                                                        | 5.6  |     |      | v     |

| VIN OVP Hysteresis                     |                      |                                                                                    |      | 300 |      | mV    |

| CH1 (4A)                               |                      |                                                                                    |      |     |      |       |

| Converter                              |                      |                                                                                    |      |     |      |       |

| VIN Quiescent Current                  | IQ_VIN               | Enable, no switching, other voltage rails off, not include I <sub>VIN</sub> .      |      | 25  | 35   | μA    |

| Output Voltage Scaling                 | Vout                 | Controlled by I <sup>2</sup> C. (Note 6)                                           | 0.7  |     | 1.3  | V     |

| DC Output Voltage<br>Programmable Step | VSTEP                |                                                                                    |      | 10  |      | mV    |

| Output Voltage Default                 | V <sub>OUT</sub>     | REFOUT = REFADJ = REFIN = VIN, refer<br>to configuration for other default voltage | 0.99 | 1   | 1.01 | V     |

| Dynamic Voltage Scale<br>Slew Rate     |                      |                                                                                    |      | 5   |      | mV/μs |

| Line Regulation                        |                      | (Note 5)                                                                           |      | 0.5 |      | %/V   |

| Parameter                         | Symbol                 | Test Conditions                                                        | Min   | Тур  | Max   | Unit |

|-----------------------------------|------------------------|------------------------------------------------------------------------|-------|------|-------|------|

| Load Regulation                   |                        | Force PWM (Note 5)                                                     |       | 0.5  |       | %/A  |

| H/S Switch On<br>Resistance       | RDS(ON)_H              | PVIN1 = 5V                                                             |       | 36   |       | mΩ   |

| L/S Switch On Resistance          | RDS(ON)_L              | PVIN1 = 5V                                                             |       | 27   |       | mΩ   |

| Current Limit                     | ILIM                   | Valley current                                                         | 4.1   | 5    |       | А    |

| Switching Frequency               | fsw                    |                                                                        | 1.8   | 2    | 2.2   | MHz  |

| Minimum Off-Time                  | toff_min               |                                                                        |       | 120  | 160   | ns   |

| OVP Trip Threshold                | VOVP                   | OVP detected                                                           | 120   | 125  | 130   | %    |

| OVP Propagation Delay<br>(Note 5) | tovpdly                |                                                                        |       | 1    |       | μs   |

| UVP Trip Threshold                | Vuvp                   | UVP detected                                                           | 57.5  | 62.5 | 67.5  | %    |

| UVP Propagation Delay<br>(Note 5) | tuvpdly                |                                                                        |       | 2    |       | μs   |

| PGOOD Trip Threshold              |                        | Falling edge, measured at CH1 VOUT                                     | 80    | 85   | 90    | %    |

| PGOOD Trip Hysteresis             |                        |                                                                        |       | 5    |       | %    |

| Soft-Start Time                   | tss                    | VOUT1 = 1V                                                             |       | 0.5  | 0.8   | ms   |

| Discharge Resistance              | RDISCHG                | $V_{IN}$ = 5V, discharge from LX1                                      |       | 10   |       | Ω    |

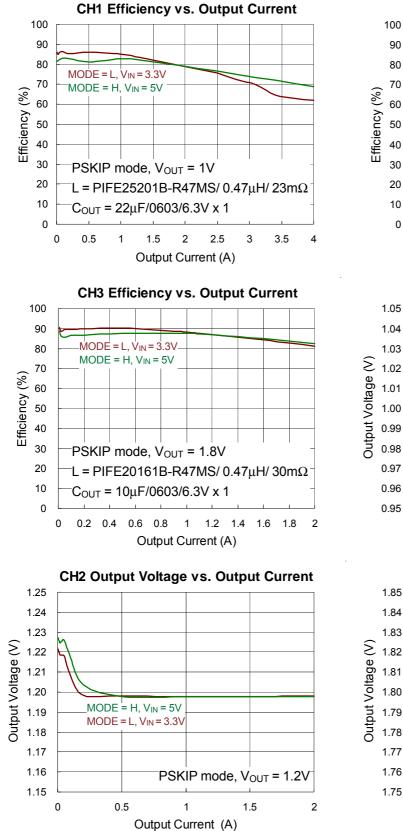

|                                   |                        | PVIN1 = 3.3V, VOUT1 = 1V,<br>I <sub>OUT</sub> = 10mA                   | 85    |      |       | %    |

| Efficiency                        |                        | PVIN1 = 3.3V, VOUT1 = 1V,<br>Iout = 1A                                 | 85    |      |       | %    |

| REFOUT Buffer                     | I                      |                                                                        |       |      |       |      |

| Quiescent Current                 |                        | REFOUT buffer are enabled.                                             |       | 5    |       | μA   |

| REFADJ Switch On<br>Resistance    |                        | V <sub>IN</sub> = 5V                                                   |       | 10   |       | Ω    |

| REFOUT Voltage                    | VREFOUT                | Sourcing Current = 0.05mA, with 6.8nF<br>Capacitor                     | -1%   | 1.2  | 1%    | V    |

| CH2 (2A)                          |                        |                                                                        |       |      |       |      |

| VIN Quiescent Current             | I <sub>Q_IN</sub>      | Enable, no switching, other voltage rails off, not include $I_{VIN}$ . |       | 25   | 35    | μA   |

| Internal Reference<br>Voltage     |                        | Connect FB2 to resistor voltage divider, measure at FB2 pin.           | 0.792 | 0.8  | 0.808 | V    |

|                                   | N/                     | FB2 connected to VOUT2 for RT5091A                                     |       | 1.35 |       |      |

| Output Voltage Default            | Vout                   | FB2 connected to VOUT2 for RT5091B                                     |       | 1.2  |       | V    |

| Line Regulation                   |                        | (Note 5)                                                               | -     | 0.5  |       | %/V  |

| Load Regulation                   |                        | Force PWM (Note 5)                                                     |       | 0.5  |       | %/A  |

| H/S Switch On<br>Resistance       | R <sub>DS(ON)</sub> _H | PVIN2 = 5V                                                             |       | 103  |       | mΩ   |

| L/S Switch On Resistance          | R <sub>DS(ON)</sub> _L | PVIN2 = 5V                                                             | 1     | 64   |       | mΩ   |

| Parameter                         | Symbol           | Test Conditions                                                        | Min   | Тур  | Max   | Unit |

|-----------------------------------|------------------|------------------------------------------------------------------------|-------|------|-------|------|

| Current Limit                     | ILIM             | Valley current                                                         | 2.1   | 3    |       | А    |

| Switching Frequency               | fsw              |                                                                        | 1.8   | 2    | 2.2   | MHz  |

| Minimum Off-Time                  | toff_min         |                                                                        |       | 120  | 160   | ns   |

| OVP Trip Threshold                | VOVP             | OVP detected                                                           | 120   | 125  | 130   | %    |

| OVP Propagation Delay<br>(Note 5) | tovpdly          |                                                                        |       | 1    |       | μS   |

| UVP Trip Threshold                | Vuvp             | UVP detected                                                           | 57.5  | 62.5 | 67.5  | %    |

| UVP Propagation Delay<br>(Note 5) | tuvpdly          |                                                                        |       | 2    |       | μS   |

| PGOOD Trip Threshold              |                  | Falling edge, measured at CH2 VOUT                                     | 80    | 85   | 90    | %    |

| PGOOD Trip Hysteresis             |                  |                                                                        |       | 5    |       | %    |

| Soft-Start Time                   | tss              |                                                                        |       | 0.5  | 0.8   | ms   |

| Discharge Resistance              | RDISCHG          | $V_{IN}$ = 5V, discharge from LX2                                      |       | 10   |       | Ω    |

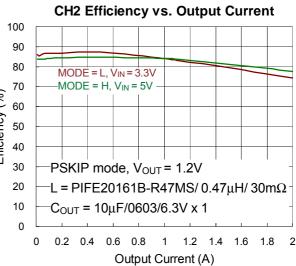

| Efficiency                        |                  | PVIN2 = 3.3V, FB2 = 1.2V,<br>I <sub>OUT</sub> = 10mA                   | 85    |      |       | %    |

| Efficiency                        |                  | PVIN2 = 3.3V, FB2 = 1.2V,<br>I <sub>OUT</sub> = 0.5A                   | 85    |      |       | %    |

| CH3 (2A)                          |                  |                                                                        |       |      |       |      |

| VIN Quiescent Current             | Iq_in            | Enable, no switching, other voltage rails off, not include $I_{VIN}$ . |       | 25   | 35    | μA   |

| Internal Reference<br>Voltage     |                  | Connect FB3 to resistor voltage divider, measure at FB3 pin.           | 0.792 | 0.8  | 0.808 | V    |

| Output Voltage Default            | Vout             | FB3 connected to CH3 VOUT                                              |       | 1.8  |       | V    |

| Line Regulation                   |                  | (Note 5)                                                               |       | 0.5  |       | %/V  |

| Load Regulation                   |                  | Force PWM (Note 5)                                                     | -     | 0.5  |       | %/A  |

| H/S Switch On<br>Resistance       | Rds(on)_H        | PVIN3 = 5V                                                             | -     | 101  |       | mΩ   |

| L/S Switch On Resistance          | Rds(on)_L        | PVIN3 = 5V                                                             |       | 58   |       | mΩ   |

| Current Limit                     | Ilim             | Valley current                                                         | 2.1   | 3    |       | А    |

| Switching Frequency               | f <sub>SW</sub>  |                                                                        | 1.8   | 2    | 2.2   | MHz  |

| Minimum Off-Time                  | toff_min         |                                                                        |       | 120  | 160   | ns   |

| OVP Trip Threshold                | V <sub>OVP</sub> | OVP detected                                                           | 120   | 125  | 130   | %    |

| OVP Propagation Delay<br>(Note 5) | tovpdly          |                                                                        |       | 1    |       | μS   |

| UVP Trip Threshold                | Vuvp             | UVP detected                                                           | 57.5  | 62.5 | 67.5  | %    |

| Parameter                         | Symbol            | Test Conditi                                             | ions                 | Min     | Тур   | Max     | Unit |

|-----------------------------------|-------------------|----------------------------------------------------------|----------------------|---------|-------|---------|------|

| UVP Propagation<br>Delay (Note 5) | tuvpdly           |                                                          |                      |         | 2     |         | μS   |

| PGOOD Trip<br>Threshold           |                   | Falling edge, measured a                                 | t CH3 VOUT           | 80      | 85    | 90      | %    |

| PGOOD Trip<br>Hysteresis          |                   |                                                          |                      |         | 5     |         | %    |

| Soft-Start Time                   | tss               |                                                          |                      |         | 0.5   | 0.8     | ms   |

| Discharge Resistance              | RDISCHG           | $V_{IN}$ = 5V, discharge from                            | LX3                  |         | 10    |         | Ω    |

| <b>Efficience</b>                 |                   | PVIN3 = 3.3V, FB3 = 1.8                                  | V, Iout = 10mA       | 85      |       |         | %    |

| Efficiency                        |                   | PVIN3 = 3.3V, FB3 = 1.8                                  | V, Iout = 0.5A       | 85      |       |         | %    |

| LDO (0.3A)                        |                   |                                                          |                      |         |       |         |      |

| VIN Quiescent<br>Current          | I <sub>Q_IN</sub> | Enable, no load, other vol<br>include I <sub>VIN</sub> . | Itage rails off, not |         | 28    | 38      | μA   |

| Internal Reference                |                   | Connect FB4 to resistor                                  | For RT5091A          | 0.81675 | 0.825 | 0.83325 |      |

| Voltage                           |                   | voltage divider, measure at FB4 pin.                     | For RT5091B          | 0.4455  | 0.45  | 0.4545  | V    |

| Output Voltage                    |                   | FB4 floating for RT5091A                                 | L                    |         | 3.3   |         | V    |

| Default                           | Vout              | FB4 floating for RT5091B                                 | 5                    |         | 1.8   |         |      |

| Line Regulation                   |                   |                                                          |                      |         | 0.5   |         | %/V  |

| Load Regulation                   |                   |                                                          |                      |         | 0.5   |         | %/A  |

| Dropout Voltage                   | VDROP             | PVIN4 = 5V, VOUT4 = 3.3<br>I <sub>OUT</sub> =300mA       | 3V,                  |         |       | 100     | mV   |

| Current Limit                     | ILIM              |                                                          |                      | 0.4     |       |         | Α    |

| UVP Trip Threshold                | Vuvp              | UVP detected                                             |                      | 55      | 60    | 65      | %    |

| UVP Propagation<br>Delay (Note 5) | tuvpdly           |                                                          |                      |         | 2     |         | μs   |

| PGOOD Trip<br>Threshold           |                   | Falling edge, measured a                                 | t VOUT4              | 80      | 85    | 90      | %    |

| PGOOD Trip<br>Hysteresis          |                   |                                                          |                      |         | 5     |         | %    |

| Soft-Start Time                   | tss               | For RT5091A, VOUT4 = 3                                   | 3.3V                 |         | 0.39  | 0.6     | me   |

|                                   | 135               | For RT5091B, VOUT4 =                                     |                      |         | 0.26  | 0.5     | ms   |

| Discharge Resistance              | RDISCHG           | $V_{IN}$ = 5V, discharge from                            | VOUT4                |         | 100   |         | Ω    |

| Power Supply                      | PSRR              | I <sub>OUT</sub> = 100mA, f = 100Hz                      |                      |         | -50   |         | dB   |

| Rejection Rate                    |                   | I <sub>OUT</sub> =100mA, f = 100kHz                      | 2                    |         | -28   |         |      |

## RT5091A/B

| Parameter                                          | Symbol              | Test Conditions                                        | Min | Тур | Max | Unit |

|----------------------------------------------------|---------------------|--------------------------------------------------------|-----|-----|-----|------|

| GPIO                                               |                     |                                                        |     |     |     |      |

| GPIO Input (VSNS)                                  |                     |                                                        |     |     |     |      |

| VSNS Discharge Resistance                          | RDISCHG             |                                                        |     | 10  |     | Ω    |

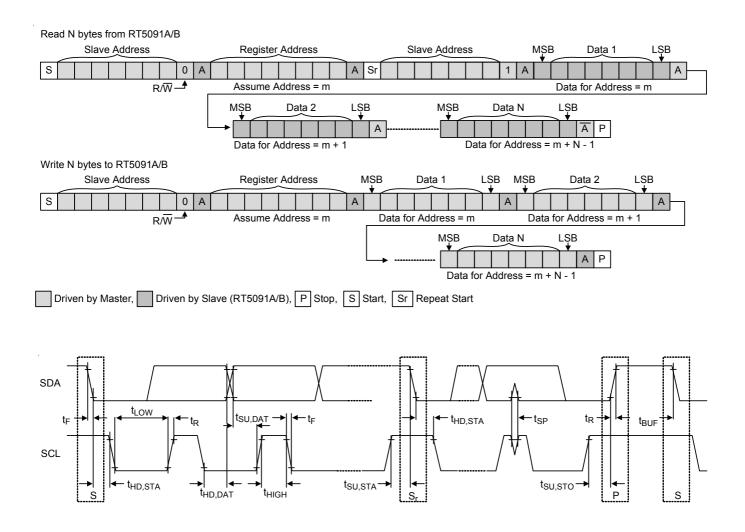

| I <sup>2</sup> C for Fast Mode                     |                     |                                                        |     |     |     |      |

| SDA, SCL Input Voltage High                        |                     |                                                        | 1.2 |     |     | V    |

| SDA, SCL Input Voltage Low                         |                     |                                                        |     |     | 0.4 | V    |

| SCL Clock Rate                                     | f <sub>SCL</sub>    |                                                        | 100 |     | 400 | kHz  |

| Hold Time for a Repeated START Condition           | thd;sta             | After this period, the first clock pulse is generated. | 0.6 |     | -   | μs   |

| Low Period of the SCL Clock                        | t∟ow                |                                                        | 1.3 |     |     | μS   |

| High Period of the SCL Clock                       | tніgн               |                                                        | 0.6 |     |     | μS   |

| Set Up Time For a Repeated START Condition         | tsu;sta             |                                                        | 0.6 |     |     | μs   |

| Data Hold Time                                     | t <sub>HD;DAT</sub> |                                                        | 0   |     | 0.9 | μS   |

| Data Set Up Time                                   | tsu;dat             |                                                        | 100 |     |     | ns   |

| Set Up Time for STOP<br>Condition                  | tsu;sto             |                                                        | 0.6 |     | 1   | μS   |

| Bus Free Time between a STOP and a START Condition | tbuf                |                                                        | 1.3 |     | 1   | μS   |

| Rising Time of Both SDA/SCL<br>Signals             | t <sub>R</sub>      |                                                        | 20  |     | 300 | ns   |

| Falling Time of Both SDA/SCL<br>Signals            | tF                  |                                                        | 20  |     | 300 | ns   |

| SDA Output Low Sink Current                        | I <sub>OL</sub>     | SDA voltage = 0.4V                                     | 2   |     |     | mA   |

| RI | CH | T | EK |

|----|----|---|----|

| _  |    | _ |    |

| Parameter                                        | Symbol              | Test Conditions                                        | Min | Тур | Max | Unit |

|--------------------------------------------------|---------------------|--------------------------------------------------------|-----|-----|-----|------|

| I <sup>2</sup> C for High Speed Mode             | I                   |                                                        |     |     |     |      |

| SDA, SCL Input Voltage<br>High                   |                     |                                                        | 1.2 |     |     | V    |

| SDA, SCL Input Voltage<br>Low                    |                     |                                                        |     |     | 0.4 | V    |

| SCL Clock Rate                                   | f <sub>SCL</sub>    |                                                        | 0.1 |     | 3.4 | MHz  |

| Hold Time for a Repeated START Condition         | thd;sta             | After this period, the first clock pulse is generated. | 160 |     |     | ns   |

| Low Period of the SCL<br>Clock                   | tLOW                |                                                        | 160 |     |     | ns   |

| High Period of the SCL<br>Clock                  | tніgн               |                                                        | 60  |     |     | ns   |

| Set-Up Time For a<br>Repeated START<br>Condition | tsu;sta             |                                                        | 60  |     |     | ns   |

| Data Hold Time                                   | t <sub>HD;DAT</sub> |                                                        | 0   |     | 70  | ns   |

| Data Set-Up Time                                 | tsu;dat             |                                                        | 10  |     |     | ns   |

| Set-Up Time for STOP<br>Condition                | tsu;sto             |                                                        | 160 |     |     | ns   |

| Rising Time of Both<br>SDA/SCL Signals           | t <sub>R</sub>      |                                                        | 10  |     | 80  | ns   |

| Falling Time of Both<br>SDA/SCL Signals          | tF                  |                                                        | 10  |     | 80  | ns   |

| SDA Output Low Sink<br>Current                   | I <sub>OL</sub>     | SDA voltage = 0.4V                                     | 2   |     |     | mA   |

- **Note 1.** Stresses beyond those listed "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2.  $\theta_{JA}$  is measured under natural convection (still air) at  $T_A = 25^{\circ}C$  with the component mounted on a high effectivethermal-conductivity four-layer test board on a JEDEC 51-7 thermal measurement standard.  $\theta_{JC}$  is measured at the exposed pad of the package.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

Note 5. Guaranteed by design.

**Note 6.** Program CH1 output voltage via I<sup>2</sup>C need default output voltage setting during power-up sequence. Please set CH1 buck converter by Table 15.

### **Typical Operating Characteristics**

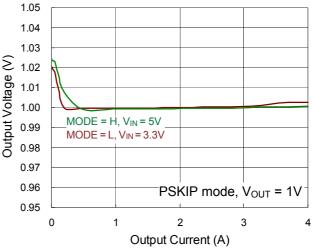

CH1 Output Voltage vs. Output Current

The contract of the second se

0

Copyright ©2017 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

2

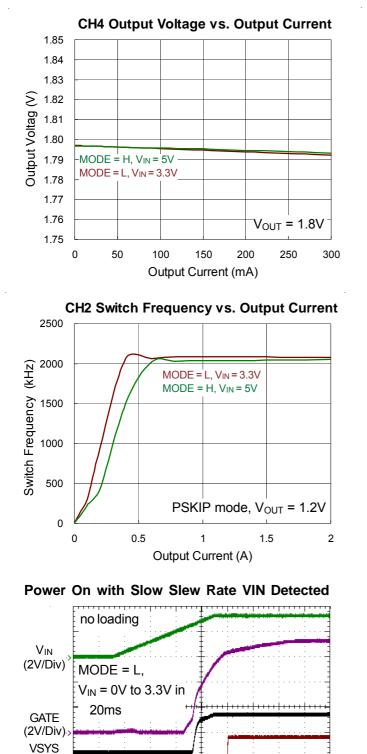

Time (5ms/Div)

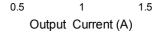

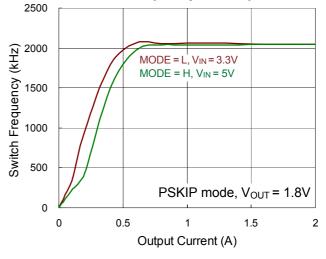

CH3 Switch Frequency vs. Output Current

Copyright ©2017 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

(2V/Div)

CH4

(1V/Div)

CH1 (500mV/Div)

> CH2 (1V/Div)

> > CH3

(1V/Div)

STANDBY (3V/Div)

PGOOD

(5V/Div)

CH1 (300mV/Div)3

LX1

(3V/Div)

**Enter/Exit Sleep Mode**

V<sub>CH1 Normal Mode</sub> = 0.9V

V<sub>CH1 Sleep Mode</sub> = 0.7V

Time (10ms/Div)

Time (5µs/Div)

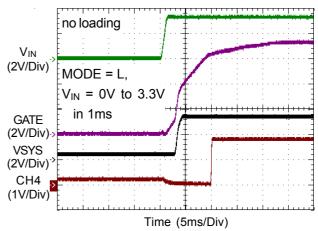

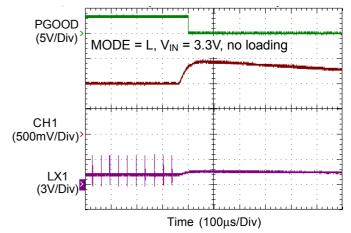

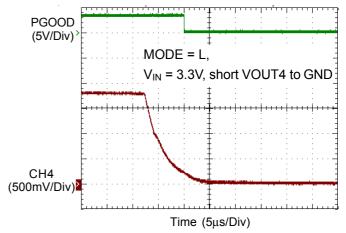

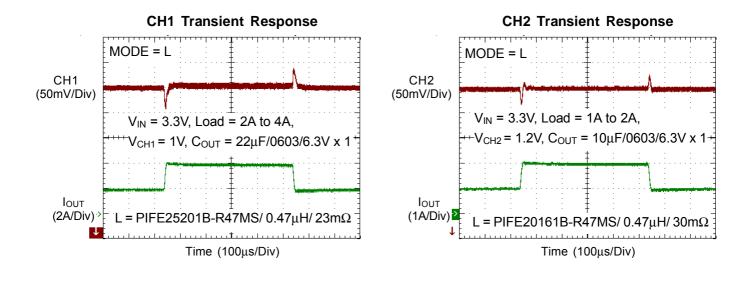

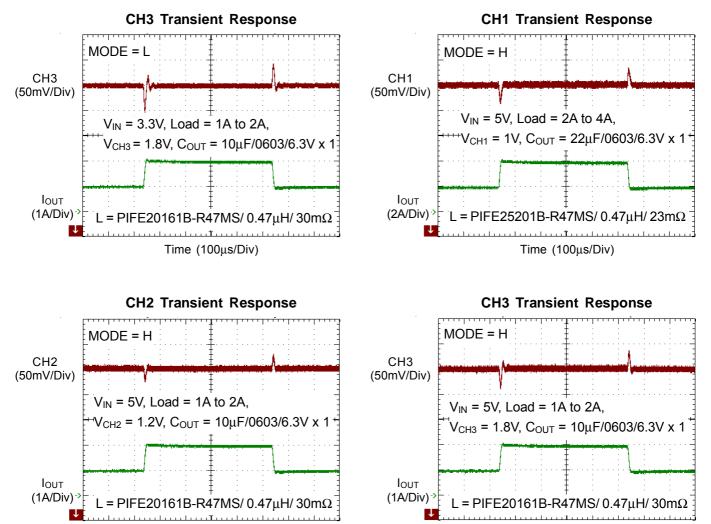

MODE = L,  $V_{IN} = 3.3V_{,}$

$V_{CH2} = 1.2V_{,}$ V<sub>CH3</sub> = 1.8V

**CH1 Over Voltage Protection**

PGOOD

(5V/Div)

CH3 (500mV/Div)

LX3

(3V/Div)

**CH3 Under Voltage Protection**

Time (5µs/Div)

V<sub>IN</sub> = 3.3V, short FB3 to GND

MODE = L,

**CH4 Under Voltage Protection**

Copyright ©2017 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

Time (100µs/Div)

Time (100µs/Div)

### **Functional Register Table**

| Name                    | Туре | Register Reset | Address Offset |

|-------------------------|------|----------------|----------------|

| STANDBY                 | R/W  | 0x00h          | 0x00           |

| PGOOD_VSYS_REG          | R/W  |                | 0x01           |

| CH1_VID_REG             | R/W  |                | 0x02           |

| DCDCCTRL0_REG0          | R/W  | 0x00h          | 0x03           |

| DCDCCTRL1_REG           | R/W  | 0x00h          | 0x04           |

| CH1/CH2_CONTROL         | R/W  | 0x56h          | 0x05           |

| CH3/LDO_CONTROL         | R/W  | 0XE1h          | 0x06           |

| EXT_EN1/EXT_EN2_CONTROL | R/W  | 0x8Ah          | 0x07           |

| PRODUCT_ID_REG          | R    | 0x00h          | 0x0A           |

| MANUFACTURER_ID_REG     | R    | 0x00h          | 0x0B           |

| REVISION_NUMBER_REG     | R    | 0x00h          | 0x0C           |

| PROTECT                 | R    |                | 0x0D           |

#### Table 2. STANDBY

| Address : 0x00<br>Description : STANDBY Mode Enable/Disable |      |                                         |   |          |   |   |   |           |  |  |  |

|-------------------------------------------------------------|------|-----------------------------------------|---|----------|---|---|---|-----------|--|--|--|

| Bits                                                        | Bit7 | Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 |   |          |   |   |   |           |  |  |  |

| Name                                                        |      |                                         |   | Reserved |   |   |   | STANDBYEN |  |  |  |

| Reset Value                                                 | 0    | 0                                       | 0 | 0        | 0 | 0 | 0 | 0         |  |  |  |

| Read/ Write                                                 | R    | R                                       | R | R        | R | R | R | R/W       |  |  |  |

| Bits  | Name      | Description                                                     |

|-------|-----------|-----------------------------------------------------------------|

| 7 : 1 | Reserved  | Reserved bit                                                    |

| 0     | STANDBYEN | Standby mode allowed to enter<br>0 : Not allowed<br>1 : Allowed |

#### Table 3. PGOOD\_VSYS\_REG

| Address : 0x01<br>Description : Power good information register<br>When voltage rails achieve 90% of VID target, the relative bit will set to 1. |                                         |               |               |               |      |            |     |          |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|---------------|---------------|---------------|------|------------|-----|----------|--|--|

| Bits                                                                                                                                             | Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 |               |               |               |      |            |     |          |  |  |

| Name                                                                                                                                             | CH1_<br>PGOOD                           | CH2_<br>PGOOD | CH3_<br>PGOOD | LDO_<br>PGOOD | MODE | VSYSRDY_TH |     | Reserved |  |  |

| Reset Value                                                                                                                                      | 0                                       | 0             | 0             | 0             |      |            |     | 1        |  |  |

| Read/ Write                                                                                                                                      | R                                       | R             | R             | R             | R    | R/W        | R/W | R/W      |  |  |

| Bits  | Name       | Description                                                                                                                                                                                                                                                                                                                                                               |

|-------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | CH1_PGOOD  | Status bit. Indicates power good on CH1                                                                                                                                                                                                                                                                                                                                   |

| 6     | CH2_PGOOD  | Status bit. Indicates power good on CH2                                                                                                                                                                                                                                                                                                                                   |

| 5     | CH3_PGOOD  | Status bit. Indicates power good on CH3                                                                                                                                                                                                                                                                                                                                   |

| 4     | LDO_PGOOD  | Status bit. Indicates power good on CH4                                                                                                                                                                                                                                                                                                                                   |

| 3     | MODE       | MODE = Low, MODE[3] = 0b<br>MODE = High, MODE[3] = 1b                                                                                                                                                                                                                                                                                                                     |

| 2 : 1 | VSYSRDY_TH | MODE = Low, MODE[3] = 0b :<br>VSYSRDY_TH[2:1] = 00b : 2.7V (default)<br>VSYSRDY_TH[2:1] = 01b : 2.8V<br>VSYSRDY_TH[2:1] = 10b : 2.9V<br>VSYSRDY_TH[2:1] = 11b : 3V<br>MODE = High, MODE[3] = 1b :<br>VSYSRDY_TH[2:1] = 00b : 3.8V (default)<br>VSYSRDY_TH[2:1] = 00b : 3.9V<br>VSYSRDY_TH[2:1] = 01b : 3.9V<br>VSYSRDY_TH[2:1] = 10b : 4V<br>VSYSRDY_TH[2:1] = 11b : 4.1V |

| 0     | Reserved   | Reserved bit. Keep it always be 1.                                                                                                                                                                                                                                                                                                                                        |

#### Table 4. CH1\_VID\_REG

| Address : 0x02<br>Description : CH1 VID setting register |          |                                         |     |     |     |     |     |     |  |

|----------------------------------------------------------|----------|-----------------------------------------|-----|-----|-----|-----|-----|-----|--|

| Bits                                                     | Bit7     | Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 |     |     |     |     |     |     |  |

| Name                                                     | Reserved |                                         | SEL |     |     |     |     |     |  |

| Reset Value                                              | 0        | 0                                       |     |     |     |     |     |     |  |

| Read/Write                                               | R        | R                                       | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Bits | Name     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6  | Reserved | Reserved bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5:0  | SEL      | Supply voltage :<br>SEL[5:0] = 000000b : 0.7V<br>SEL[5:0] = 00001b : 0.71V<br>SEL[5:0] = 000010b : 0.72V<br>SEL[5:0] = 000110b : 0.73V<br>SEL[5:0] = 000110b : 0.75V<br>SEL[5:0] = 000110b : 0.75V<br>SEL[5:0] = 001100b : 0.78V<br>SEL[5:0] = 001100b : 0.79V<br>SEL[5:0] = 001100b : 0.79V<br>SEL[5:0] = 001101b : 0.81V<br>SEL[5:0] = 001100b : 0.82V<br>SEL[5:0] = 001110b : 0.82V<br>SEL[5:0] = 001110b : 0.83V<br>SEL[5:0] = 001110b : 0.83V<br>SEL[5:0] = 001111b : 0.83V<br>SEL[5:0] = 001111b : 0.84V<br>SEL[5:0] = 001111b : 0.84V<br>SEL[5:0] = 001111b : 0.84V<br>SEL[5:0] = 010111b : 0.84V<br>SEL[5:0] = 010100b : 0.86V<br>SEL[5:0] = 010000b : 0.86V<br>SEL[5:0] = 010011b : 0.87V<br>SEL[5:0] = 010011b : 0.88V<br>SEL[5:0] = 010011b : 0.98V<br>SEL[5:0] = 010110b : 0.92V<br>SEL[5:0] = 010111b : 0.93V<br>SEL[5:0] = 011010b : 0.92V<br>SEL[5:0] = 011101b : 0.94V<br>SEL[5:0] = 011101b : 0.94V<br>SEL[5:0] = 011101b : 0.94V<br>SEL[5:0] = 011101b : 0.98V<br>SEL[5:0] = 011000b : 1.02V<br>SEL[5:0] = 100000b : 1.02V<br>SEL[5:0] = 100010b : 1.02V<br>SEL[5:0] = 100010b : 1.02V<br>SEL[5:0] = 100010b : 1.04V<br>SEL[5:0] = 100010b : 1.04V |

| Bits | Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5:0  | SEL  | $\begin{array}{l} \text{SEL}[5:0] = 100110b: 1.08V\\ \text{SEL}[5:0] = 100111b: 1.09V\\ \text{SEL}[5:0] = 101000b: 1.1V\\ \text{SEL}[5:0] = 101001b: 1.11V\\ \text{SEL}[5:0] = 101010b: 1.12V\\ \text{SEL}[5:0] = 101100b: 1.14V\\ \text{SEL}[5:0] = 101101b: 1.15V\\ \text{SEL}[5:0] = 101110b: 1.16V\\ \text{SEL}[5:0] = 101110b: 1.16V\\ \text{SEL}[5:0] = 101111b: 1.17V\\ \text{SEL}[5:0] = 10001b: 1.18V\\ \text{SEL}[5:0] = 110000b: 1.18V\\ \text{SEL}[5:0] = 110001b: 1.20V\\ \text{SEL}[5:0] = 110010b: 1.22V\\ \text{SEL}[5:0] = 110010b: 1.22V\\ \text{SEL}[5:0] = 110101b: 1.22V\\ \text{SEL}[5:0] = 110101b: 1.22V\\ \text{SEL}[5:0] = 110101b: 1.22V\\ \text{SEL}[5:0] = 110110b: 1.24V\\ \text{SEL}[5:0] = 110110b: 1.24V\\ \text{SEL}[5:0] = 110110b: 1.26V\\ \text{SEL}[5:0] = 110110b: 1.26V\\ \text{SEL}[5:0] = 111000b: 1.28V\\ \text{SEL}[5:0] = 111001b: 1.28V\\ \text{SEL}[5:0] = 111100b: 1.28V\\ \text$ |

#### Table 5. DCDCCTRL0\_REG0

| Address : 0x03<br>Description : Internal enable register |                                      |            |            |            |            |                |                |          |  |  |  |

|----------------------------------------------------------|--------------------------------------|------------|------------|------------|------------|----------------|----------------|----------|--|--|--|

| Bits                                                     | BitsBit7Bit6Bit5Bit4Bit3Bit2Bit1Bit0 |            |            |            |            |                |                |          |  |  |  |

| Name                                                     | LSW1_<br>EN                          | CH1_<br>EN | CH2_<br>EN | CH3_<br>EN | LDO_<br>EN | EXT_EN1_<br>EN | EXT_EN2_<br>EN | Reserved |  |  |  |

| Reset Value                                              | 0                                    | 0          | 0          | 0          | 0          | 0              | 0              | 0        |  |  |  |

| Read/Write                                               | R/W                                  | R/W        | R/W        | R/W        | R/W        | R/W            | R/W            | R        |  |  |  |

| Bits | Name       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | LSW1_EN    | LSW1_EN[7] = 0b : Disable LSW1<br>LSW1_EN[7] = 1b : Enable LSW1<br>After PMIC powering up, this register value is auto-written to 1b. Power off<br>all rails by setting 0b, PMIC will automatically set this register to 0x00h.<br>Setting to 1b will re-power on all rails in sequence, DO NOT set this register<br>to any value other than 0x80h. In case of rails are forced to be turned on<br>during internal circuits are still doing the auto-calibration and detecting<br>progress. |

| 6    | CH1_EN     | CH1_EN[6] = 0b : Disable CH1<br>CH1_EN[6] = 1b : Enable CH1<br>After PMIC powering up, this register value is auto-written to 1b.                                                                                                                                                                                                                                                                                                                                                           |

| 5    | CH2_EN     | CH2_EN[5] = 0b : Disable CH2<br>CH2_EN[5] = 1b : Enable CH2<br>After PMIC powering up, this register value is auto-written to 1b.                                                                                                                                                                                                                                                                                                                                                           |

| 4    | CH3_EN     | CH3_EN[4] = 0b : Disable CH3<br>CH3_EN[4] = 1b : Enable CH3<br>After PMIC powering up, this register value is auto-written to 1b.                                                                                                                                                                                                                                                                                                                                                           |

| 3    | LDO_EN     | LDO_EN[3] = 0b : Disable LDO<br>LDO_EN[3] = 1b : Enable LDO<br>After PMIC powering up, this register value is auto-written to 1b.                                                                                                                                                                                                                                                                                                                                                           |

| 2    | EXT_EN1_EN | EXT_EN1_EN[2] = 0b : Disable EXT_EN1<br>EXT_EN2_EN[2] = 1b : Enable EXT_EN1<br>After PMIC powering up, this register value is auto-written to 1b.                                                                                                                                                                                                                                                                                                                                           |

| 1    | EXT_EN2_EN | CH6_EN[1] = 0b : Disable EXT_EN2<br>CH6_EN[1] = 1b : Enable EXT_EN2<br>After PMIC powering up, this register value is auto-written to 1b.                                                                                                                                                                                                                                                                                                                                                   |

| 0    | Reserved   | Reserved bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

#### Table 6. DCDCCTRL1\_REG

| Address : 0x04 Description : DCDC PSKIP/PWM mode control register |             |             |             |          |      |      |      |      |  |

|-------------------------------------------------------------------|-------------|-------------|-------------|----------|------|------|------|------|--|

| Bits                                                              | Bit7        | Bit6        | Bit5        | Bit4     | Bit3 | Bit2 | Bit1 | Bit0 |  |

| Name                                                              | CH1_<br>PWM | CH2_<br>PWM | CH3_<br>PWM | Reserved |      |      |      |      |  |

| Reset Value                                                       | 0           | 0           | 0           | 0        | 0    | 0    | 0    | 0    |  |

| Read/Write                                                        | R/W         | R/W         | R/W         | R        | R    | R    | R    | R    |  |

| Bits | Name     | Description                                                       |

|------|----------|-------------------------------------------------------------------|

| 7    | CH1_PWM  | CH1_PWM[7] = 0b : PSKIP mode<br>CH1_PWM[7] = 1b : Forced PWM mode |

| 6    | CH2_PWM  | CH2_PWM[6] = 0b : PSKIP mode<br>CH2_PWM[6] = 1b : Forced PWM mode |

| 5    | CH3_PWM  | CH3_PWM[5] = 0b : PSKIP mode<br>CH3_PWM[5] = 1b : Forced PWM mode |

| 4:0  | Reserved | Reserved bit                                                      |

#### Table 7. CH1\_CH2\_CONTROL

|             | Address : 0x05<br>Description : CH1/CH2 wake up timing configure register & sleep mode control register      |     |     |           |                     |     |     |           |  |  |  |  |  |