# Dual-Output PWM Controller with 3 Integrated Drivers for AMD SVI2 Mobile CPU Power Supply

### **General Description**

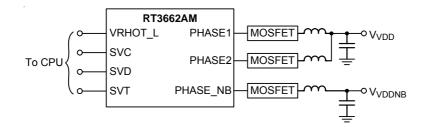

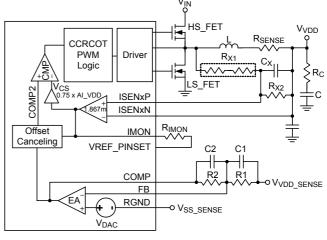

The RT3662AM is a dual-output PWM controller with 3 integrated drivers, and it is compliant with AMD SVI2 Voltage Regulator Specification to support both CPU core (VDD) and Northbridge portion of CPU (VDDNB). The RT3662AM features CCRCOT (Constant Current Ripple Constant On-Time) with G-NAVP (Green-Native AVP), which is Richtek' s proprietary topology. G-NAVP makes it an easy setting controller to meet all AMD AVP (Adaptive Voltage Positioning) VDD/VDDNB requirements. The droop is easily programmed by setting the DC gain of the error amplifier. With proper compensation, the load transient response can achieve optimized AVP performance. The controller also uses the interface to issue VOTF Complete and to send digitally encoded voltage and current values for the VDD/VDDNB domains. The RT3662AM can operate in diode emulation mode to enhance the light load efficiency. And it provides the current gain adjustment capability by pin setting. The RT3662AM provides power good indication, thermal indication (VRHOT L), and it features complete fault protection functions including over current, over voltage and under voltage.

### Features

- 2/1-Phase (VDD) + 1/0-Phase (VDDNB) PWM Controller

- 3 Embedded MOSFET Drivers

- G-NAVP<sup>™</sup> Topology

- Support Dynamic Load-Line and Zero Load-Line

- Diode Emulation Mode at Light Load Condition

- SVI2 Interface to Comply with AMD Power Management Protocol

- Adjustable Current Gain Capability

- DVID Enhancement

- 0.5% DAC Accuracy

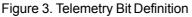

- Differential Remote Voltage Sensing

- Build-in ADC for Pin Setting Programming, Thermal Indication and V<sub>OUT</sub>, I<sub>OUT</sub> Reporting

- Fast Transient Response

- Power Good Indicator

- Thermal Indicator (VRHOT\_L)

- OVP, UVP and UVLO

- Over Current Protection

### Applications

- AMD SVI2 Mobile CPU

- Laptop Computer

### **Simplified Application Circuit**

### **Ordering Information**

RT3662AM 🖵 📮

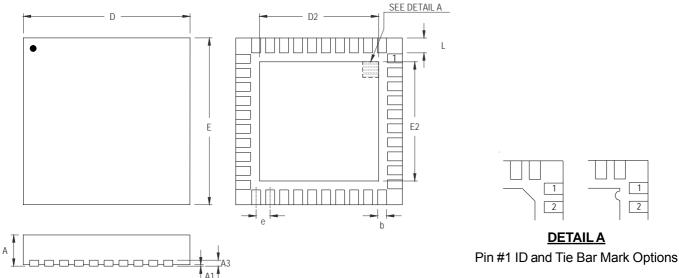

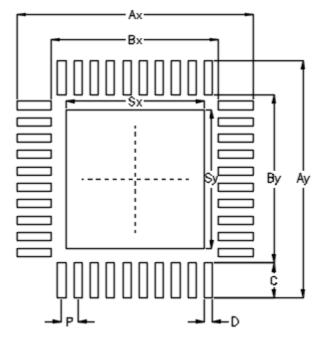

Package Type QW : WQFN-40L 5x5 (W-Type) —Lead Plating System G : Green (Halogen Free and Pb Free)

Note :

Richtek products are :

- RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- Suitable for use in SnPb or Pb-free soldering processes.

### **Marking Information**

RT3662AM GQW YMDNN RT3662AMGQW : Product Number YMDNN : Date Code

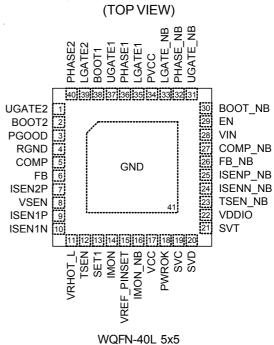

### **Pin Configuration**

| Pin No | Pin Name | Pin Function                                                                                                                                                                                                                                                                                                               |

|--------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | UGATE2   | Upper gate driver output of Phase 2 for VDD controller. Connect this pin to the gate input of high side MOSFET.                                                                                                                                                                                                            |

| 2      | BOOT2    | Bootstrap supply of VDD controller for Phase 2 high side MOSFET. This pin powers high side MOSFET driver.                                                                                                                                                                                                                  |

| 3      | PGOOD    | Power good indicator for the VDD and VDDNB controller. This pin is an open drain output.                                                                                                                                                                                                                                   |

| 4      | RGND     | Return ground of VDD and VDDNB controllers. This pin is the common negative input of output voltage differential remote sense of VDD and VDDNB controllers.                                                                                                                                                                |

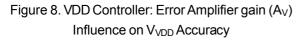

| 5      | COMP     | Error amplifier output pin of the VDD controller.                                                                                                                                                                                                                                                                          |

| 6      | FB       | Output voltage feedback input of VDD controller. This pin is the negative input of the error amplifier for the VDD controller.                                                                                                                                                                                             |

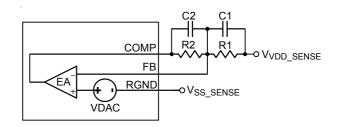

| 7      | ISEN2P   | Positive current sense input of Phase 2 for VDD controller.                                                                                                                                                                                                                                                                |

| 8      | VSEN     | VDD controller voltage sense input. This pin is connected to the terminal of VDD controller output voltage.                                                                                                                                                                                                                |

| 9      | ISEN1P   | Positive current sense input of Phase 1 for VDD controller.                                                                                                                                                                                                                                                                |

| 10     | ISEN1N   | Common negative current sense input of Phase1 and Phase 2 for VDD controller.                                                                                                                                                                                                                                              |

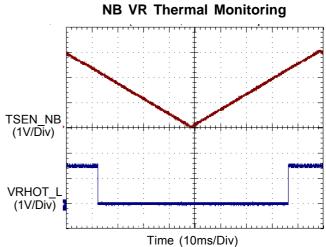

| 11     | VRHOT_L  | Thermal indicator. This pin is an open drain output. (Active low)                                                                                                                                                                                                                                                          |

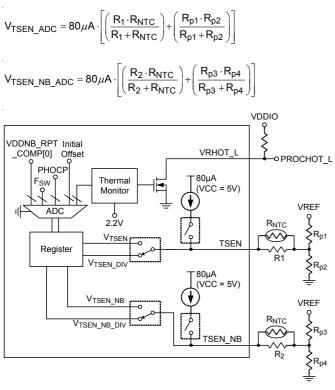

| 12     | TSEN     | This pin provides two functions: platform setting, platform can use this pin to set<br>frequency of VDD and VDDNB controllers, initial offset and per-phase OCP<br>threshold of VDD controller. The other function is thermal sense input for<br>VRHOT indicator. Connect the NTC network for thermal sensing to this pin. |

### **Functional Pin Description**

| Pin No | Pin Name    | Pin Function                                                                                                                                                                                                                                                                                                                                                                                |

|--------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

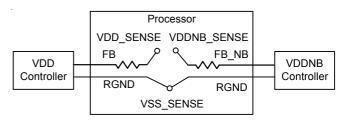

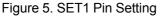

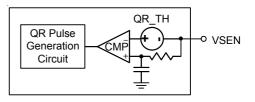

| 13     | SET1        | Platform setting pin. Platform can use this pin to set the Ai gain of VDD and VDDNB controllers, VDDNB voltage reporting compensation bit1 to bit3 and VDD Controller QRTH.                                                                                                                                                                                                                 |

| 14     | IMON        | Current monitor output for the VDD controller. This pin outputs a voltage proportional to the output current.                                                                                                                                                                                                                                                                               |

| 15     | VREF_PINSET | This pin provides two functions: The 3.2V power supply for pin setting function divided resistors. The other function is fixed 0.8V output reference voltage, and the voltage is only used to offset the output voltage of IMON and IMON_NB pins. Connect a RC circuit from this pin to GND. The recommended resistor is from $3.9\Omega$ to $10\Omega$ , and the capacitor is $0.47\mu$ F. |

| 16     | IMON_NB     | Current monitor output for the VDDNB controller. This pin outputs a voltage proportional to the output current.                                                                                                                                                                                                                                                                             |

| 17     | VCC         | Controller power supply. Connect this pin to 5V and place a decoupling capacitor $2.2\mu$ F at least. The decoupling capacitor is as close controller as possible.                                                                                                                                                                                                                          |

| 18     | PWROK       | System power good input. If PWROK is low, the SVI interface is disabled and VR returns to BOOT-VID state with initial load-line slope and initial offset. If PWROK is high, the SVI interface is running and the DAC decodes the received serial VID codes to determine the output voltage.                                                                                                 |

| 19     | SVC         | Serial VID clock input.                                                                                                                                                                                                                                                                                                                                                                     |

| 20     | SVD         | Serial VID data input. This pin is a serial data line.                                                                                                                                                                                                                                                                                                                                      |

| 21     | SVT         | Serial VID telemetry output from VR. This pin is a push-pull output.                                                                                                                                                                                                                                                                                                                        |

| 22     | VDDIO       | Processor memory interface power rail and serves as the reference for PWROK, SVD, SVC and SVT. This pin is used by the VR to reference the SVI pins.                                                                                                                                                                                                                                        |

| 23     | TSEN_NB     | This pin provides two functions: platform setting, platform can use this pin to set initial offset, BOOT VID, voltage reporting compensation bit0 and per-<br>phase OCP threshold of VDDNB controller. The other function is thermal sense input for VRHOT indicator. Connect the NTC network for thermal sensing to this pin.                                                              |

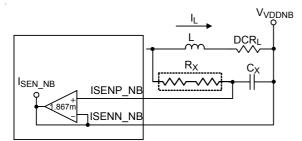

| 24     | ISENN_NB    | Negative current sense input for VDDNB controller.                                                                                                                                                                                                                                                                                                                                          |

| 25     | ISENP_NB    | Positive current sense input for VDDNB controller.                                                                                                                                                                                                                                                                                                                                          |

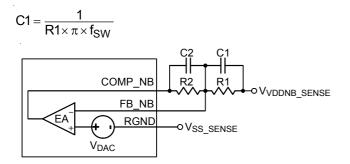

| 26     | FB_NB       | Output voltage feedback input of VDDNB controller. This pin is the negative input of the error amplifier for the VDDNB controller.                                                                                                                                                                                                                                                          |

| 27     | COMP_NB     | Error amplifier output pin of the VDDNB controller.                                                                                                                                                                                                                                                                                                                                         |

| 28     | VIN         | VIN input pin. Connect a low pass filter to this pin.                                                                                                                                                                                                                                                                                                                                       |

| 29     | EN          | Controller enable input pin.                                                                                                                                                                                                                                                                                                                                                                |

| 30     | BOOT_NB     | Bootstrap supply of VDDNB controller for high side MOSFET. This pin powers high side MOSFET driver.                                                                                                                                                                                                                                                                                         |

| 31     | UGATE_NB    | Upper gate driver output of VDDNB controller. Connect this pin to the gate input of high side MOSFET.                                                                                                                                                                                                                                                                                       |

| 32     | PHASE_NB    | Switch nodes of high side driver for VDDNB controller. Connect this pin to high side MOSFET source together with the low side MOSFET drain and the inductor.                                                                                                                                                                                                                                |

| 33     | LGATE_NB    | Lower gate driver output of VDDNB controller. Connect this pin to the gate input of low side MOSFET.                                                                                                                                                                                                                                                                                        |

| 34     | PVCC        | Driver power supply. Connect this pin to GND by the $2.2\mu$ F ceramic capacitor at least. The decoupling capacitor is as close controller as possible.                                                                                                                                                                                                                                     |

| Pin No              | Pin Name | Pin Function                                                                                                                                                       |

|---------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 35                  | LGATE1   | Lower gate driver output of Phase 1 for VDD controller. Connect this pin to the gate input of low side MOSFET.                                                     |

| 36                  | PHASE1   | Phase 1 switch nodes of high side driver for VDD controller. Connect this pin to high side MOSFET source together with the low side MOSFET drain and the inductor. |

| 37                  | UGATE1   | Upper gate driver output of Phase 1 for VDD controller. Connect this pin to the gate input of high side MOSFET.                                                    |

| 38                  | BOOT1    | Bootstrap supply of VDD controller for Phase 1 high side MOSFET. This pin powers high side MOSFET driver.                                                          |

| 39                  | LGATE2   | Lower gate driver output of Phase 2 for VDD controller. Connect this pin to the gate input of low side MOSFET.                                                     |

| 40                  | PHASE2   | Phase 2 switch nodes of high side driver for VDD controller. Connect this pin to high side MOSFET Source together with the low side MOSFET drain and the inductor. |

| 41<br>(Exposed Pad) | GND      | Ground. The exposed pad must be soldered to a large PCB and connected to GND for maximum power dissipation.                                                        |

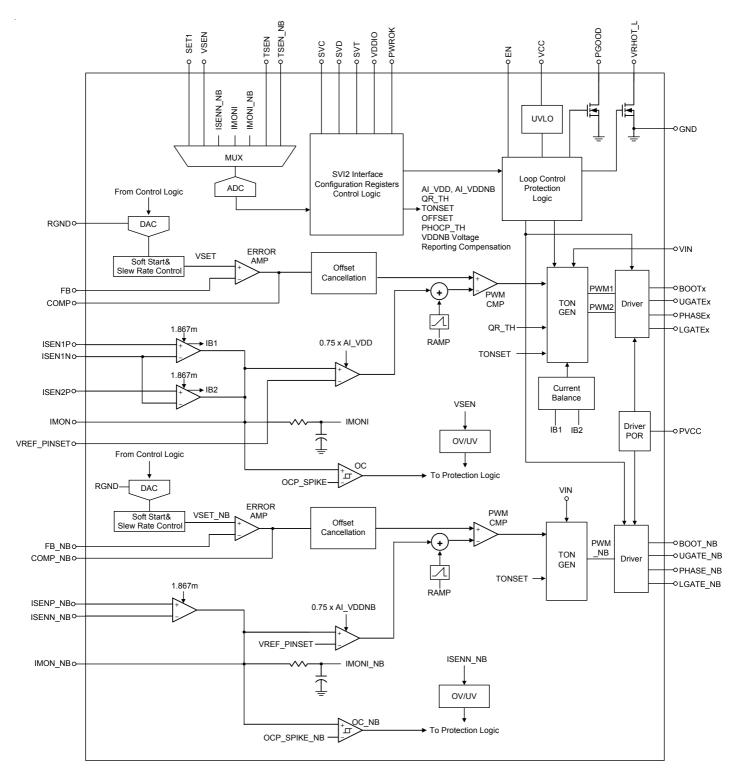

### **Functional Block Diagram**

### Operation

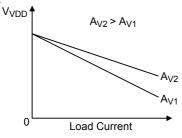

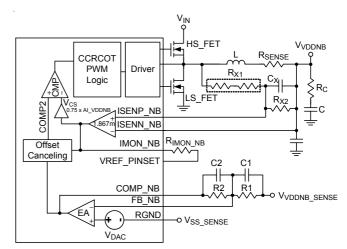

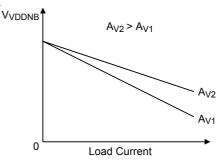

The RT3662AM adopts G-NAVP<sup>™</sup> (Green Native AVP) which is Richtek' s proprietary topology derived from finite DC gain of EA amplifier with current mode control, making it easy to set the droop to meet all AMD CPU requirements of AVP (Adaptive Voltage Positioning). The G-NAVP<sup>™</sup> controller is one type of current mode constant on-time control with DC offset cancellation. The approach can not only improve DC offset problem for increasing system accuracy but also provide fast transient response. When current feedback signal reaches COMP signal, it generates an on-time width to achieve PWM modulation.

#### MUX and ADC

The MUX supports the inputs from SET1, TSEN, TSEN\_NB, IMONI, IMONI\_NB, ISENN\_NB and VSEN. The ADC converts these analog signals to digital codes for reporting or performance adjustment.

#### SVI2 Interface/Configuration Registers/Control Logic

The SVI2 interface uses the SVC, SVD, and SVT pins to communicate with CPU. The configuration registers save the digital data from ADC output for reporting or performance adjustment. The Control Logic controls the ADC timing and generates the digital code of the VID for VDD/VDDNB voltage.

#### **Loop Control Protection Logic**

Loop control protection logic detects EN and UVLO signals to initiate the soft-start function, and the PGOOD and VRHOT\_L will be controlled after the soft-start is finished. When VRHOT indication event occurs, the VRHOT\_L pin voltage will be pulled low.

#### DAC

The DAC receives VID codes from the SVI2 control logic to generate an internal reference voltage (VSET/VSET\_NB) for controller.

#### Soft-Start and Slew-Rate Control

This block controls the slew rate of the internal reference voltage when output voltage changes.

#### Error Amplifier

Error amplifier generates COMP/COMP\_NB signal by the difference between VSET/VSET\_NB and FB/FB\_NB.

#### **Offset Cancellation**

This block cancels the output offset voltage from voltage ripple and current ripple to achieve accurate output voltage.

#### UVLO

Detect the VCC pin voltage for under voltage lockout protection and power on reset operation.

#### **Current Balance**

Each phase current sense signal is sent to the current balance circuit which adjusts the on-time of each phase to optimize current sharing.

#### **PWM CMP**

The PWM comparator compares COMP signal (COMP/ COMP\_NB) and current feedback signal to generate a signal for TONGEN.

#### TONGEN

This block generates an on-time pulse which high interval is based on the on-time setting.

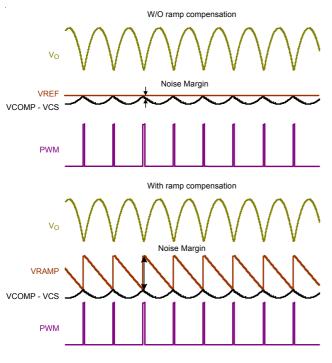

#### RAMP

The Ramp generator is designed to improve noise immunity and reduce jitter.

#### OC/OV/UV

Output voltage and output current are sensed for over current, over voltage and under voltage protection.

|            |             |            | Table 1. Ser | ial VID Codes |             |            |             |

|------------|-------------|------------|--------------|---------------|-------------|------------|-------------|

| SVID [7:0] | Voltage (V) | SVID [7:0] | Voltage (V)  | SVID [7:0]    | Voltage (V) | SVID [7:0] | Voltage (V) |

| 0000_0000  | 1.55000     | 0010_0111  | 1.30625      | 0100_1110     | 1.06250     | 0111_0101  | 0.81875     |

| 0000_0001  | 1.54375     | 0010_1000  | 1.30000      | 0100_1111     | 1.05625     | 0111_0110  | 0.81250     |

| 0000_0010  | 1.53750     | 0010_1001  | 1.29375      | 0101_0000     | 1.05000     | 0111_0111  | 0.80625     |

| 0000_0011  | 1.53125     | 0010_1010  | 1.28750      | 0101_0001     | 1.04375     | 0111_1000  | 0.80000     |

| 0000_0100  | 1.52500     | 0010_1011  | 1.28125      | 0101_0010     | 1.03750     | 0111_1001  | 0.79375     |

| 0000_0101  | 1.51875     | 0010_1100  | 1.27500      | 0101_0011     | 1.03125     | 0111_1010  | 0.78750     |

| 0000_0110  | 1.51250     | 0010_1101  | 1.26875      | 0101_0100     | 1.02500     | 0111_1011  | 0.78125     |

| 0000_0111  | 1.50625     | 0010_1110  | 1.26250      | 0101_0101     | 1.01875     | 0111_1100  | 0.77500     |

| 0000_1000  | 1.50000     | 0010_1111  | 1.25625      | 0101_0110     | 1.01250     | 0111_1101  | 0.76875     |

| 0000_1001  | 1.49375     | 0011_0000  | 1.25000      | 0101_0111     | 1.00625     | 0111_1110  | 0.76250     |

| 0000_1010  | 1.48750     | 0011_0001  | 1.24375      | 0101_1000     | 1.00000     | 0111_1111  | 0.75625     |

| 0000_1011  | 1.48125     | 0011_0010  | 1.23750      | 0101_1001     | 0.99375     | 1000_0000  | 0.75000     |

| 0000_1100  | 1.47500     | 0011_0011  | 1.23125      | 0101_1010     | 0.98750     | 1000_0001  | 0.74375     |

| 0000_1101  | 1.46875     | 0011_0100  | 1.22500      | 0101_1011     | 0.98125     | 1000_0010  | 0.73750     |

| 0000_1110  | 1.46250     | 0011_0101  | 1.21875      | 0101_1100     | 0.97500     | 1000_0011  | 0.73125     |

| 0000_1111  | 1.45625     | 0011_0110  | 1.21250      | 0101_1101     | 0.96875     | 1000_0100  | 0.72500     |

| 0001_0000  | 1.45000     | 0011_0111  | 1.20625      | 0101_1110     | 0.96250     | 1000_0101  | 0.71875     |

| 0001_0001  | 1.44375     | 0011_1000  | 1.20000      | 0101_1111     | 0.95625     | 1000_0110  | 0.71250     |

| 0001_0010  | 1.43750     | 0011_1001  | 1.19375      | 0110_0000     | 0.95000     | 1000_0111  | 0.70625     |

| 0001_0011  | 1.43125     | 0011_1010  | 1.18750      | 0110_0001     | 0.94375     | 1000_1000  | 0.70000     |

| 0001_0100  | 1.42500     | 0011_1011  | 1.18125      | 0110_0010     | 0.93750     | 1000_1001  | 0.69375     |

| 0001_0101  | 1.41875     | 0011_1100  | 1.17500      | 0110_0011     | 0.93125     | 1000_1010  | 0.68750     |

| 0001_0110  | 1.41250     | 0011_1101  | 1.16875      | 0110_0100     | 0.92500     | 1000_1011  | 0.68125     |

| 0001_0111  | 1.40625     | 0011_1110  | 1.16250      | 0110_0101     | 0.91875     | 1000_1100  | 0.67500     |

| 0001_1000  | 1.40000     | 0011_1111  | 1.15625      | 0110_0110     | 0.91250     | 1000_1101  | 0.66875     |

| 0001_1001  | 1.39375     | 0100_0000  | 1.15000      | 0110_0111     | 0.90625     | 1000_1110  | 0.66250     |

| 0001_1010  | 1.38750     | 0100_0001  | 1.14375      | 0110_1000     | 0.90000     | 1000_1111  | 0.65625     |

| 0001_1011  | 1.38125     | 0100_0010  | 1.13750      | 0110_1001     | 0.89375     | 1001_0000  | 0.65000     |

| 0001_1100  | 1.37500     | 0100_0011  | 1.13125      | 0110_1010     | 0.88750     | 1001_0001  | 0.64375     |

| 0001_1101  | 1.36875     | 0100_0100  | 1.12500      | 0110_1011     | 0.88125     | 1001_0010  | 0.63750     |

| 0001_1110  | 1.36250     | 0100_0101  | 1.11875      | 0110_1100     | 0.87500     | 1001_0011  | 0.63125     |

| 0001_1111  | 1.35625     | 0010_0110  | 1.11250      | 0110_1101     | 0.86875     | 1001_0100  | 0.62500     |

| 0010_0000  | 1.35000     | 0100_0111  | 1.10625      | 0110_1110     | 0.86250     | 1001_0101  | 0.61875     |

| 0010_0001  | 1.34375     | 0100_1000  | 1.10000      | 0110_1111     | 0.85625     | 1001_0110  | 0.61250     |

| 0010_0010  | 1.33750     | 0100_1001  | 1.09375      | 0111_0000     | 0.85000     | 1001_0111  | 0.60625     |

| 0010_0011  | 1.33125     | 0100_1010  | 1.08750      | 0111_0001     | 0.84375     | 1001_1000  | 0.60000     |

| 0010_0100  | 1.32500     | 0100_1011  | 1.08125      | 0111_0010     | 0.83750     | 1001_1001  | 0.59375     |

| 0010_0101  | 1.31875     | 0100_1100  | 1.07500      | 0111_0011     | 0.83125     | 1001_1010  | 0.58750     |

| 0010_0110  | 1.31250     | 0100_1101  | 1.06875      | 0111_0100     | 0.82500     | 1001_1011  | 0.58125     |

Table 1. Serial VID Codes

Copyright ©2019 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

DS3662AM-00 July 2019

| SVID [7:0]  | Voltage (V) | SVID [7:0]  | Voltage (V) | SVID [7:0]  | Voltage (V) | SVID [7:0] | Voltage (V) |

|-------------|-------------|-------------|-------------|-------------|-------------|------------|-------------|

| 1001_1100   | 0.57500     | 1011_0101 * | 0.41875     | 1100_1110 * | 0.26250     | 1110_0111* | 0.10625     |

| 1001_1101   | 0.56875     | 1011_0110 * | 0.41250     | 1100_1111 * | 0.25625     | 1110_1000* | 0.10000     |

| 1001_1110   | 0.56250     | 1011_0111 * | 0.40625     | 1101_0000 * | 0.25000     | 1110_1001* | 0.09375     |

| 1001_1111   | 0.55625     | 1011_1000 * | 0.40000     | 1101_0001 * | 0.24375     | 1110_1010* | 0.08750     |

| 1010_0000   | 0.55000     | 1011_1001 * | 0.39375     | 1101_0010 * | 0.23750     | 1110_1011* | 0.08125     |

| 1010_0001   | 0.54375     | 1011_1010 * | 0.38750     | 1101_0011 * | 0.23125     | 1110_1100* | 0.07500     |

| 1010_0010   | 0.53750     | 1011_1011 * | 0.38125     | 1101_0100 * | 0.22500     | 1110_1101* | 0.06875     |

| 1010_0011   | 0.53125     | 1011_1100 * | 0.37500     | 1101_0101 * | 0.21875     | 1110_1110* | 0.06250     |

| 1010_0100   | 0.52500     | 1011_1101 * | 0.36875     | 1101_0110 * | 0.21250     | 1110_1111* | 0.05625     |

| 1010_0101   | 0.51875     | 1011_1110 * | 0.36250     | 1101_0111 * | 0.20625     | 1111_0000* | 0.05000     |

| 1010_0110   | 0.51250     | 1011_1111 * | 0.35625     | 1101_1000 * | 0.20000     | 1111_0001* | 0.04375     |

| 1010_0111   | 0.50625     | 1100_0000 * | 0.35000     | 1101_1001 * | 0.19375     | 1111_0010* | 0.03750     |

| 1010_1000 * | 0.50000     | 1100_0001 * | 0.34375     | 1101_1010 * | 0.18750     | 1111_0011* | 0.03125     |

| 1010_1001 * | 0.49375     | 1100_0010 * | 0.33750     | 1101_1011 * | 0.18125     | 1111_0100* | 0.02500     |

| 1010_1010 * | 0.48750     | 1100_0011 * | 0.33125     | 1101_1100 * | 0.17500     | 1111_0101* | 0.01875     |

| 1010_1011 * | 0.48125     | 1100_0100 * | 0.32500     | 1101_1101 * | 0.16875     | 1111_0110* | 0.01250     |

| 1010_1100 * | 0.47500     | 1100_0101 * | 0.31875     | 1101_1110 * | 0.16250     | 1111_0111* | 0.00625     |

| 1010_1101 * | 0.46875     | 1100_0110 * | 0.31250     | 1101_1111 * | 0.15625     | 1111_1000* | 0.00000     |

| 1010_1110 * | 0.46250     | 1100_0111 * | 0.30625     | 1110_0000*  | 0.15000     | 1111_1001* | OFF         |

| 1010_1111 * | 0.45625     | 1100_1000 * | 0.30000     | 1110_0001*  | 0.14375     | 1111_1010* | OFF         |

| 1011_0000 * | 0.45000     | 1100_1001 * | 0.29375     | 1110_0010*  | 0.13750     | 1111_1011* | OFF         |

| 1011_0001 * | 0.44375     | 1100_1010 * | 0.28750     | 1110_0011*  | 0.13125     | 1111_1100* | OFF         |

| 1011_0010 * | 0.43750     | 1100_1011 * | 0.28125     | 1110_0100*  | 0.12500     | 1111_1101* | OFF         |

| 1011_0011 * | 0.43125     | 1100_1100 * | 0.27500     | 1110_0101*  | 0.11875     | 1111_1110* | OFF         |

| 1011_0100 * | 0.42500     | 1100_1101 * | 0.26875     | 1110_0110*  | 0.11250     | 1111_1111* | OFF         |

\* Indicates TOB is 80mV for this VID code; unconditional VR controller stability required at all VID codes

| SET1 Pin Se | etting Voltage | $V_{SET1_{DIV}} = 3.2$ | $\times \frac{R_D}{R_U + R_D}$ | AI_VDD | VDDNB_RPT_OFS<br>[3:1] bits |

|-------------|----------------|------------------------|--------------------------------|--------|-----------------------------|

| Min         | Typical        | Max                    | Unit                           |        |                             |

| 6.75        | 25             | 43.25                  | mV                             |        | 000                         |

| 57.25       | 75             | 92.75                  | mV                             |        | 001                         |

| 107.75      | 125            | 142.25                 | mV                             |        | 010                         |

| 158.25      | 175            | 191.75                 | mV                             | 250/   | 011                         |

| 208.75      | 225            | 241.25                 | mV                             | - 25%  | 100                         |

| 259.25      | 275            | 290.75                 | mV                             |        | 101                         |

| 309.75      | 325            | 340.25                 | mV                             | ]      | 110                         |

| 360.25      | 375            | 389.75                 | mV                             |        | 111                         |

| 410.75      | 425            | 439.25                 | mV                             |        | 000                         |

| 461.25      | 475            | 488.75                 | mV                             |        | 001                         |

| 511.75      | 525            | 538.25                 | mV                             |        | 010                         |

| 562.25      | 575            | 587.75                 | mV                             | -      | 011                         |

| 612.75      | 625            | 637.25                 | mV                             | 50%    | 100                         |

| 663.25      | 675            | 686.75                 | mV                             |        | 101                         |

| 713.75      | 725            | 736.25                 | mV                             |        | 110                         |

| 764.25      | 775            | 785.75                 | mV                             |        | 111                         |

| 814.75      | 825            | 835.25                 | mV                             |        | 000                         |

| 865.25      | 875            | 884.75                 | mV                             |        | 001                         |

| 915.75      | 925            | 934.25                 | mV                             |        | 010                         |

| 966.25      | 975            | 983.75                 | mV                             |        | 011                         |

| 1016.75     | 1025           | 1033.25                | mV                             | - 100% | 100                         |

| 1067.25     | 1075           | 1082.75                | mV                             | -      | 101                         |

| 1117.75     | 1125           | 1132.25                | mV                             | 1      | 110                         |

| 1168.25     | 1175           | 1181.75                | mV                             | 1      | 111                         |

| 1218.75     | 1225           | 1231.25                | mV                             |        | 000                         |

| 1269.25     | 1275           | 1280.75                | mV                             | 1      | 001                         |

| 1319.75     | 1325           | 1330.25                | mV                             | 1      | 010                         |

| 1370.25     | 1375           | 1379.75                | mV                             | 1      | 011                         |

| 1420.75     | 1425           | 1429.25                | mV                             | - OLL  | 100                         |

| 1471.25     | 1475           | 1478.75                | mV                             |        | 101                         |

| 1521.75     | 1525           | 1528.25                | mV                             | 1      | 110                         |

| 1572.25     | 1575           | 1577.75                | mV                             | 1      | 111                         |

| SET1 Pin Set | ting Voltage $\left( V \right)$ | / <sub>SET1_IR</sub> = 80μ | AI_VDDNB  | QR Threshold<br>(VDD) |         |

|--------------|---------------------------------|----------------------------|-----------|-----------------------|---------|

| Min          | Typical                         | Max                        | Unit      |                       |         |

| 7.84         | 50                              | 92.16                      |           |                       | Disable |

| 213.2        | 250                             | 286.8                      |           | 25%                   | 20mV    |

| 315.88       | 350                             | 384.12                     |           |                       | 25mV    |

| 418.56       | 450                             | 481.44                     |           |                       | Disable |

| 623.92       | 650                             | 676.08                     | 50%<br>mV | 20mV                  |         |

| 726.6        | 750                             | 773.4                      |           |                       | 25mV    |

| 829.28       | 850                             | 870.72                     |           |                       | Disable |

| 1034.64      | 1050                            | 1065.36                    |           | 100%                  | 20mV    |

| 1137.32      | 1150                            | 1162.68                    |           |                       | 25mV    |

| 1240         | 1250                            | 1260                       |           |                       | Disable |

| 1445.36      | 1450                            | 1454.64                    |           | OLL                   | 20mV    |

| 1548.04      | 1550                            | 1551.96                    |           |                       | 25mV    |

#### Table 3. SET1 Pin Setting for VDDNB Controller AI Gain Ratio, VDD Controller QR Threshold

# Table 4. TSEN Pin Setting for the Frequency of VDD/VDDNB Controller, VDD Controller Initial Offset and PHOCP Setting Ratio

| <b>TSEN Pin Setting Voltage</b> $\left(V_{TSEN_{DIV}} = 3.2 \times \frac{R_{D}}{R_{U} + R_{D}}\right)$ |               |               |               | Frequency<br>(VDD/VDDNB) | Initial Offset<br>(VDD) | VDD PHOCP<br>Setting Ratio<br>(Percentage of |

|--------------------------------------------------------------------------------------------------------|---------------|---------------|---------------|--------------------------|-------------------------|----------------------------------------------|

| Min                                                                                                    | Typical       | Max           | Unit          |                          |                         | OCP_SPIKE)                                   |

| 6.75                                                                                                   | 25            | 43.25         | mV            |                          | –25mV                   | 150%                                         |

| 57.25                                                                                                  | 75            | 92.75         | mV            |                          | -25IIIV                 | 200%                                         |

| 208.75                                                                                                 | 225           | 241.25        | mV            |                          | 0mV                     | 150%                                         |

| 259.25                                                                                                 | 275           | 290.75        | mV            | 20064                    | UIIV                    | 200%                                         |

| 410.75                                                                                                 | 425           | 439.25        | mV            | - 300kHz                 | 25mV                    | 150%                                         |

| 461.25                                                                                                 | 475           | 488.75        | mV            |                          | 251117                  | 200%                                         |

| 612.75                                                                                                 | 625           | 637.25        | mV            |                          | 50mV                    | 150%                                         |

| 663.25                                                                                                 | 675           | 686.75        | mV            |                          |                         | 200%                                         |

| 814.75                                                                                                 | 825           | 835.25        | mV            |                          | 25m)/                   | 150%                                         |

| 865.25                                                                                                 | 875           | 884.75        | mV            |                          | –25mV                   | 200%                                         |

| 1016.75                                                                                                | 1025          | 1033.25       | mV            |                          | 0m)/                    | 150%                                         |

| 1067.25                                                                                                | 1075          | 1082.75       | mV            | 400kHz                   | 0mV                     | 200%                                         |

| 1218.75                                                                                                | 1225          | 1231.25       | mV            | 400KHZ                   | 25mV                    | 150%                                         |

| 1269.25                                                                                                | 1275          | 1280.75       | mV            | ]                        | 201110                  | 200%                                         |

| 1420.75                                                                                                | 1425          | 1429.25       | mV            | ]                        | 50m)/                   | 150%                                         |

| 1471.25                                                                                                | 1475          | 1478.75       | mV            |                          | 50mV                    | 200%                                         |

| PHOCP_TH =                                                                                             | OCP_SPIKE × ( | PHOCP Setting | Ratio) / M (M | I : Phase Number)        |                         |                                              |

Table 5. TSEN\_NB Pin Setting for VDDNB Controller Initial Offset, Voltage Reporting Offset and PHOCP

|         | —           | U                                                       |      | ing Ratio                 |                       | g onset and FHOCF                              |

|---------|-------------|---------------------------------------------------------|------|---------------------------|-----------------------|------------------------------------------------|

| (       | EN_NB Pin S | Setting Voltage<br>= $3.2 \times \frac{R_D}{R_U + R_U}$ | _)   | Initial Offset<br>(VDDNB) | VDDNB_RPT<br>_OFS [0] | VDDNB PHOCP<br>Setting Ratio<br>(Percentage of |

| Min     | Typical     | Max                                                     | Unit |                           |                       | OCP_SPIKE_NB)                                  |

| 6.75    | 25          | 43.25                                                   | mV   |                           |                       | 150%                                           |

| 57.25   | 75          | 92.75                                                   | mV   |                           | 0                     | 200%                                           |

| 107.75  | 125         | 142.25                                                  | mV   | (PS0)                     |                       | 150%                                           |

| 158.25  | 175         | 191.75                                                  | mV   |                           | 1                     | 200%                                           |

| 208.75  | 225         | 241.25                                                  | mV   |                           |                       | 150%                                           |

| 259.25  | 275         | 290.75                                                  | mV   | 0mV                       | 0                     | 200%                                           |

| 309.75  | 325         | 340.25                                                  | mV   | (PS0)                     |                       | 150%                                           |

| 360.25  | 375         | 389.75                                                  | mV   |                           | 1                     | 200%                                           |

| 410.75  | 425         | 439.25                                                  | mV   |                           | 0                     | 150%                                           |

| 461.25  | 475         | 488.75                                                  | mV   | 25mV                      | 0                     | 200%                                           |

| 511.75  | 525         | 538.25                                                  | mV   | (PS0)                     |                       | 150%                                           |

| 562.25  | 575         | 587.75                                                  | mV   |                           | 1                     | 200%                                           |

| 612.75  | 625         | 637.25                                                  | mV   | 50mV<br>(PS0)             | 0                     | 150%                                           |

| 663.25  | 675         | 686.75                                                  | mV   |                           |                       | 200%                                           |

| 713.75  | 725         | 736.25                                                  | mV   |                           | 1                     | 150%                                           |

| 764.25  | 775         | 785.75                                                  | mV   | -                         | 1                     | 200%                                           |

| 814.75  | 825         | 835.25                                                  | mV   |                           | 0                     | 150%                                           |

| 865.25  | 875         | 884.75                                                  | mV   | Fixed 1.5V                | 0                     | 200%                                           |

| 915.75  | 925         | 934.25                                                  | mV   | (PS2)                     | 4                     | 150%                                           |

| 966.25  | 975         | 983.75                                                  | mV   |                           | 1                     | 200%                                           |

| 1016.75 | 1025        | 1033.25                                                 | mV   |                           | 0                     | 150%                                           |

| 1067.25 | 1075        | 1082.75                                                 | mV   | Fixed 1.35V               | 0                     | 200%                                           |

| 1117.75 | 1125        | 1132.25                                                 | mV   | (PS2)                     | 1                     | 150%                                           |

| 1168.25 | 1175        | 1181.75                                                 | mV   |                           | 1                     | 200%                                           |

| 1218.75 | 1225        | 1231.25                                                 | mV   |                           | 0                     | 150%                                           |

| 1269.25 | 1275        | 1280.75                                                 | mV   | Fixed 1.25V               | 0                     | 200%                                           |

| 1319.75 | 1325        | 1330.25                                                 | mV   | (PS2)                     | 1                     | 150%                                           |

| 1370.25 | 1375        | 1379.75                                                 | mV   |                           | 1                     | 200%                                           |

| 1420.75 | 1425        | 1429.25                                                 | mV   |                           | 0                     | 150%                                           |

| 1471.25 | 1475        | 1478.75                                                 | mV   | 0mV                       | 0                     | 200%                                           |

| 1521.75 | 1525        | 1528.25                                                 | mV   | (PS2)                     | 1                     | 150%                                           |

| 1572.25 | 1575        | 1577.75                                                 | mV   |                           | 1                     | 200%                                           |

| VDDNB_RPT_OFS [3:0]                                                                                           | VDDNB Voltage Reporting Offset<br>(VDDNB_RPT_OFS) (Bits) |

|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 0000                                                                                                          | DIMON_NB x 1/128                                         |

| 0001                                                                                                          | DIMON_NB x 2/128                                         |

| 0010                                                                                                          | DIMON_NB x 3/128                                         |

| 0011                                                                                                          | DIMON_NB x 4/128                                         |

| 0100                                                                                                          | DIMON_NB x 5/128                                         |

| 0101                                                                                                          | DIMON_NB x 6/128                                         |

| 0110                                                                                                          | DIMON_NB x 7/128                                         |

| 0111                                                                                                          | DIMON_NB x 8/128                                         |

| 1000                                                                                                          | DIMON_NB x 9/128                                         |

| 1001                                                                                                          | DIMON_NB x 10/128                                        |

| 1010                                                                                                          | DIMON_NB x 11/128                                        |

| 1011                                                                                                          | DIMON_NB x 12/128                                        |

| 1100                                                                                                          | DIMON_NB x 13/128                                        |

| 1101                                                                                                          | DIMON_NB x 14/128                                        |

| 1110                                                                                                          | DIMON_NB x 15/128                                        |

| 1111                                                                                                          | DIMON_NB x 16/128                                        |

| DIMON_NB = $\frac{V_{IMON_NB} - 0.8}{0.8} \times 255$ (Bits)<br>DIMON_NB : VDDNB Current Reporting Digital Co |                                                          |

### Absolute Maximum Ratings (Note 1)

| 3                                              |               |

|------------------------------------------------|---------------|

| VCC to GND                                     | –0.3V to 6.5V |

| PVCC to GND                                    | –0.3V to 6.5V |

| • RGND to GND                                  | –0.3V to 0.3V |

| BOOTx to PHASEx                                |               |

| DC                                             | –0.3V to 6.8V |

| < 100ns                                        | –5V to 7.5V   |

| PHASEx to GND                                  |               |

| DC                                             | –0.3V to 32V  |

| < 100ns                                        | –10V to 38V   |

| UGATEx to PHASEx                               |               |

| DC                                             | 0.3V to 6.8V  |

| < 100ns                                        |               |

| LGATEx to GND                                  |               |

| DC                                             | 0.3V to 6.8V  |

| < 100ns                                        | 2.5V to 7.5V  |

| • VIN to GND                                   |               |

| • Other Pins                                   |               |

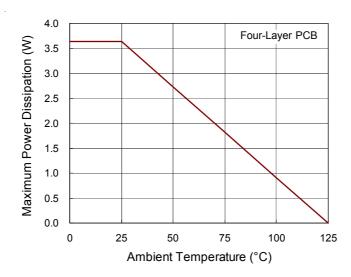

| • Power Dissipation, $P_D @ T_A = 25^{\circ}C$ |               |

| WQFN-40L 5x5                                   | 3 63W         |

| Package Thermal Resistance (Note 2)            |               |

| WQFN-40L 5x5, θ <sub>JA</sub>                  | 27 5°C/W      |

| WQFN-40L 5x5, θ <sub>JC</sub>                  |               |

| Junction Temperature                           |               |

| Lead Temperature (Soldering, 10 sec.)          |               |

| Storage Temperature Range                      |               |

| ESD Susceptibility (Note 3)                    |               |

| HBM (Human Body Model)                         | 2と/           |

|                                                | Διν           |

### Recommended Operating Conditions (Note 4)

| Supply Voltage, VCC        | 4.5V to 5.5V   |

|----------------------------|----------------|

| Supply Voltage, PVCC       | 4.5V to 5.5V   |

| Supply Voltage, VIN        | 4.5V to 24V    |

| Junction Temperature Range | –40°C to 125°C |

### **Electrical Characteristics**

(V<sub>CC</sub> = 5V,  $T_A$  = 25°C, unless otherwise specified)

| Param                  | eter         | Symbol                                                     | Test Conditions                                            | Min   | Тур  | Max   | Unit  |

|------------------------|--------------|------------------------------------------------------------|------------------------------------------------------------|-------|------|-------|-------|

| Input Power S          | Supply       |                                                            |                                                            |       |      |       | -     |

| Supply Voltage         | e            | V <sub>CC</sub>                                            |                                                            | 4.5   | 5    | 5.5   | V     |

| Supply Curren          | t            | lvcc                                                       | V <sub>EN</sub> = 3V, not switching                        |       | 9    | 15    | mA    |

| Shutdown Current       |              | I <sub>SHDN</sub>                                          | V <sub>EN</sub> = 0V                                       |       | 5    |       | μA    |

| PVCC Supply Voltage    |              | V <sub>PVCC</sub>                                          |                                                            | 4.5   | 5    | 5.5   | V     |

|                        |              | IPVCC                                                      | $V_{BOOTX}$ = 5V, not switching                            |       | 150  |       | μA    |

| Input Power S          | Supply       | 1                                                          |                                                            |       | 1    |       | ·     |

| Driver POR Threshold   |              | V <sub>POR_r</sub>                                         | PVCC POR rising                                            |       | 3.85 | 4.1   | V     |

|                        |              | V <sub>POR_f</sub>                                         | PVCC POR falling                                           | 3.4   | 3.65 |       | V     |

| Driver POR Hysteresis  |              | VPOR_Hys                                                   |                                                            | 100   | 200  | 350   | mV    |

| Reference an           | d DAC        |                                                            |                                                            |       |      |       |       |

| Reference Vol          | tage Output  | V <sub>REF</sub>                                           |                                                            | 0.795 | 0.8  | 0.805 | V     |

| DAC Accuracy           |              | V <sub>DAC</sub> = 1.0000 to 1.5500<br>(No load, CCM mode) |                                                            | -0.5  | 0    | 0.5   | %SVID |

|                        |              | VFB                                                        | V <sub>DAC</sub> = 0.8000 to 1.0000                        | -5    | 0    | 5     | mV    |

|                        |              |                                                            | V <sub>DAC</sub> = 0.3000 to 0.8000                        | -8    | 0    | 8     | mV    |

|                        |              |                                                            | V <sub>DAC</sub> = 0.2500 to 0.3000                        | -80   | 0    | 80    | mV    |

| RGND Curren            | t            | Irgnd                                                      | EN = 3V, Not switching                                     | 150   | 200  | 250   | μA    |

| Slew Rate              |              |                                                            |                                                            |       |      |       |       |

| Dynamic VID S          | Slew Rate    | SR                                                         | Set VID fast                                               | 7.5   | 10   | 15    | mV/μs |

| Error Amplifie         | er           |                                                            |                                                            |       |      |       |       |

| Input Offset           |              | VEAOFS                                                     |                                                            | -4    |      | 4     | mV    |

| DC Gain                |              | ADC                                                        | R <sub>L</sub> = 47kΩ                                      | 70    | 80   |       | dB    |

| Gain-Bandwidth Product |              | GBW                                                        | C <sub>LOAD</sub> = 5pF                                    |       | 5    |       | MHz   |

| Output Voltage Range   |              | VCOMP                                                      | $R_{LOAD} = 47 k\Omega$                                    | 0.3   |      | 3.6   | V     |

| EA Source/Sink Current |              | IEA,SRC/EA,SNK                                             | V <sub>COMP</sub> = 2V                                     |       | 5    |       | mA    |

| Current Sens           | ing Amplifie | er                                                         |                                                            |       |      |       | -     |

| Input Offset Vo        | oltage       | Voscs                                                      |                                                            | -0.4  |      | 0.4   | mV    |

| Impedance              | Negative     | RISENXN                                                    |                                                            | 1     |      |       | MΩ    |

| Input                  |              |                                                            | 1                                                          |       |      | MΩ    |       |

|                        |              | VISEN_IN                                                   | V <sub>DAC</sub> = 1.1V, (ISENxP – ISENxN)                 | -40   |      | 40    | mV    |

| Current Sense          | Gain Error   | AISEN_Err                                                  | V <sub>DAC</sub> = 1.1V                                    | -2    |      | 2     | %     |

| EN and Logic           | Inputs       |                                                            |                                                            |       |      |       |       |

| ENI Threaded           |              | VIH_EN                                                     | V <sub>IN</sub> = 10V, V <sub>DAC</sub> = 1V, Freq. = 400k | 2     |      |       | V     |

| EN Threshold           |              | VIL_EN                                                     | V <sub>DAC</sub> = 1                                       |       |      | 0.8   | V     |

| Leakage Curre          | nt of EN     | ILEK_EN                                                    | Lower limit to 1V                                          | -1    |      | 1     | μA    |

| Parameter                             | Symbol             | Test Conditions                                                                  | Min   | Тур  | Max   | Unit |

|---------------------------------------|--------------------|----------------------------------------------------------------------------------|-------|------|-------|------|

|                                       | VIH_SVI            | Respect to VDDIO                                                                 | 70    |      | 100   | %    |

| SVC, SVD, PWROK                       | VIH_SVI            | Respect to VDDIO                                                                 | 0     |      | 35    | %    |

| Hysteresis of SVC, SVD,<br>PWROK      | VHYS_SVI           | Respect to VDDIO                                                                 | 10    |      |       | %    |

| SVI2 Bus                              |                    |                                                                                  |       |      |       |      |

| SVC Frequency                         | fsvc               | (Note 5)                                                                         | 0.1   |      | 30    | MHz  |

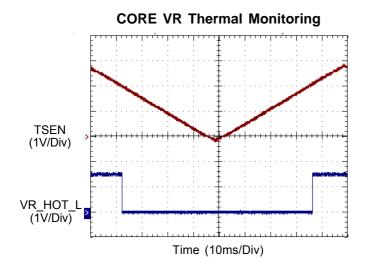

| Thermal Management                    |                    |                                                                                  |       |      |       |      |

| VRHOT Indicator Threshold             | VTH_VRHOT          |                                                                                  | 2.16  | 2.2  | 2.24  | V    |

| VRHOT Indicator Hysteresis            | VHYS_VRHOT         |                                                                                  | 50    | 75   | 100   | mV   |

| TON Setting                           | •                  |                                                                                  |       |      |       |      |

| On-Time Setting                       | t <sub>ON</sub>    | V <sub>IN</sub> = 19V,V <sub>DAC</sub> = 1V,<br>[PSI0_L:PSI1_L] = 11<br>(Note 6) | 150   | 175  | 200   | ns   |

| Minimum Off Time                      | toff               | V <sub>DAC</sub> = 1V                                                            |       | 250  | 400   | ns   |

| ITSEN                                 |                    |                                                                                  |       |      |       |      |

| TSEN Source Current                   | ITSEN              | V <sub>CC</sub> = 5V                                                             |       | 80   |       | μA   |

| Protection                            | •                  |                                                                                  |       |      |       |      |

| Under Voltage Lockout<br>Threshold    | V <sub>UVLO</sub>  | VCC falling edge                                                                 | 3.9   | 4.1  | 4.3   | V    |

| Under Voltage Lockout<br>Hysteresis   | ΔV <sub>UVLO</sub> |                                                                                  |       | 200  |       | mV   |

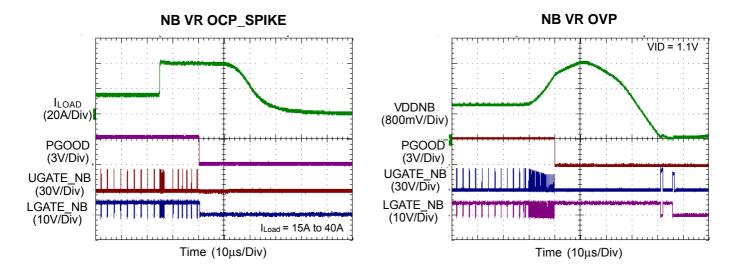

| Over Voltage Protection<br>Threshold  | V <sub>OVP</sub>   |                                                                                  | 1.8   | 1.85 | 1.9   | V    |

| Delay of OVP                          | tovp               | VSEN rising above threshold                                                      | 0.3   | 1    | 3     | μS   |

| Under Voltage Protection<br>Threshold | V <sub>UVP</sub>   | Respect to VID voltage                                                           | -600  | -500 | -400  | mV   |

| Delay of UVP                          | t <sub>UVP</sub>   | VSEN falling below threshold                                                     | 0.5   | 3    | 7     | μS   |

| OCP_SPIKE Threshold                   | IOCP_SPIKE         | DCR = 1.1mΩ, KAG = 0.6, RIMON<br>= 8.433kΩ                                       | 73.15 | 77   | 80.85 | А    |

| OCP_SPIKE Trigger Delay               | tocpspike<br>_DLY  |                                                                                  | 8     | 14   | 20    | μS   |

| Delay of Per Phase OCP                | tрноср             |                                                                                  | 0.1   | 0.5  | 1     | μS   |

| VRHOT_L and PGOOD                     |                    | ·                                                                                |       |      |       |      |

| Output Low Voltage at<br>VRHOT_L      | VVRHOT_L           | IVRHOT_L = 4mA                                                                   | 0     |      | 0.2   | V    |

| VRHOT_L Assertion Time                | <b>t</b> VRHOTL    |                                                                                  | 2     |      |       | μS   |

| Output Low Voltage at PGOOD           | Vpgood             | IPGOOD = 4mA                                                                     | 0     |      | 0.2   | V    |

| PGOOD Threshold                       | Vth_pgood          | Respect to BOOT VID                                                              |       | -300 |       | mV   |

| PGOOD Delay Time                      | tpgood             | BOOT VID to PGOOD high                                                           | 60    | 110  | 160   | μS   |

| Parameter                                     | Symbol                | Test Conditions           | Min | Тур  | Мах | Unit               |

|-----------------------------------------------|-----------------------|---------------------------|-----|------|-----|--------------------|

| Current Report                                |                       |                           |     |      |     |                    |

| Maximum Reported Current<br>(FFh = OCP_SPIKE) |                       |                           |     | 100  |     | %IDD_SP<br>IKE_OCP |

| Minimum Reported Current (00h)                |                       |                           |     | 0    |     | %IDD_SP<br>IKE_OCP |

| IDDSPIKE Current Accuracy                     |                       |                           |     |      | 3   | %                  |

| Voltage Report                                |                       |                           |     |      |     |                    |

| Maximum Reported Voltage (0_00h)              |                       |                           |     | 3.15 |     | V                  |

| Minimum Reported Voltage<br>(1_F8h)           |                       |                           |     | 0    | -   | V                  |

| Voltage Accuracy                              |                       |                           | -2  |      | 2   | LSB                |

| Switching Time                                |                       |                           |     |      |     |                    |

| UGATEx Rise Time                              | <b>t</b> UGATEr       | 3nF load                  |     | 8    |     | ns                 |

| UGATEx Fall Time                              | <b>t</b> UGATEf       | 3nF load                  |     | 8    |     | ns                 |

| LGATEx Rise Time                              | <b>t</b> LGATEr       | 3nF load                  |     | 8    |     | ns                 |

| LGATEx Fall Time                              | <b>t</b> LGATEf       | 3nF load                  |     | 4    |     | ns                 |

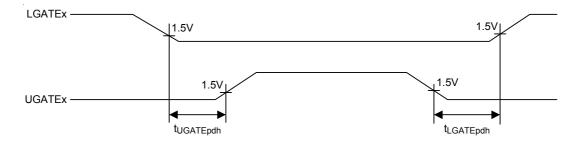

| UGATEx Turn-On Propagation<br>Delay           | tUGATEpdh             | Output unloaded           |     | 20   |     | ns                 |

| LGATEx Turn-On Propagation<br>Delay           | t <sub>LGATEpdh</sub> | Output unloaded           |     | 20   |     | ns                 |

| Output                                        |                       |                           |     |      |     |                    |

| UGATEx Driver Source<br>Resistance            | RUGATEsr              | 100mA source current      |     | 1    |     | Ω                  |

| UGATEx Driver Source<br>Current               | IUGATEsr              | VUGATE – VPHASE = 2.5V    |     | 2    |     | А                  |

| UGATEx Driver Sink<br>Resistance              | RUGATEsk              | 100mA sink current        |     | 1    |     | Ω                  |

| UGATEx Driver Sink Current                    | IUGATEsk              | VUGATE – VPHASE = 2.5V    |     | 2    |     | A                  |

| LGATEx Driver Source<br>Resistance            | RLGATEsr              | 100mA source current      |     | 1    |     | Ω                  |

| LGATEx Driver Source Current                  | ILGATEsr              | VLGATE = 2.5V             |     | 2    |     | A                  |

| LGATEx Driver Sink Resistance                 | RLGATEsk              | 100mA sink current        |     | 0.5  | -   | Ω                  |

| LGATEx Driver Sink Current                    | I <sub>LGATEsk</sub>  | V <sub>LGATE</sub> = 2.5V |     | 4    |     | A                  |

- Note 1. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2.  $\theta_{JA}$  is measured under natural convection (still air) at  $T_A = 25^{\circ}C$  with the component mounted on a high effectivethermal-conductivity four-layer test board on a JEDEC 51-7 thermal measurement standard.  $\theta_{JC}$  is measured at the exposed pad of the package.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

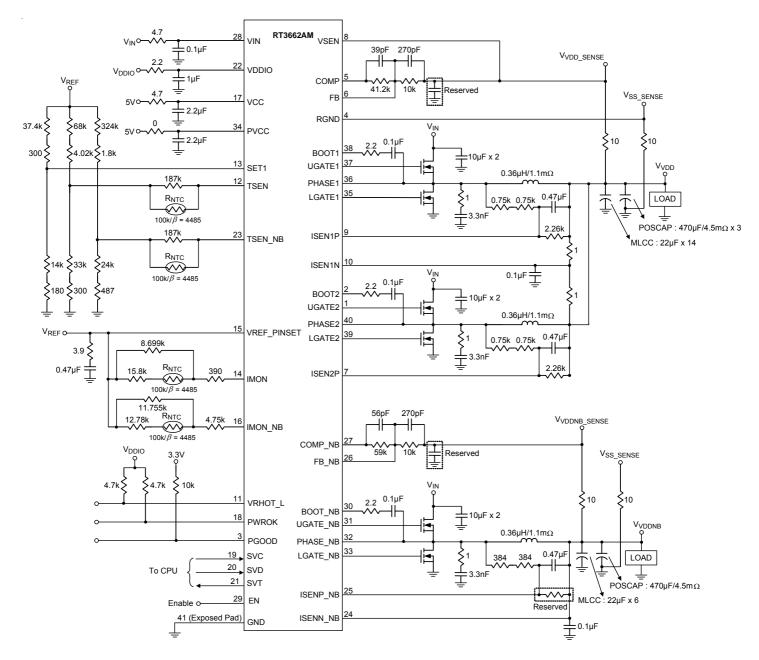

### **Typical Application Circuit**

### **Timing Diagram**

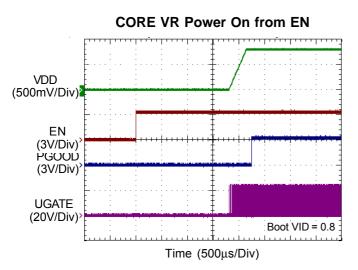

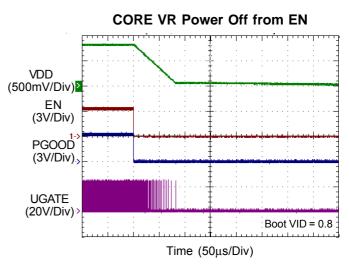

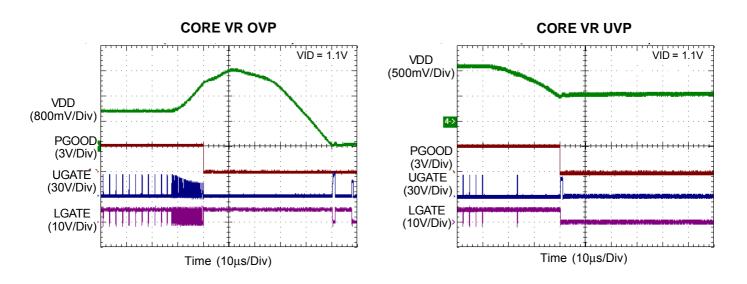

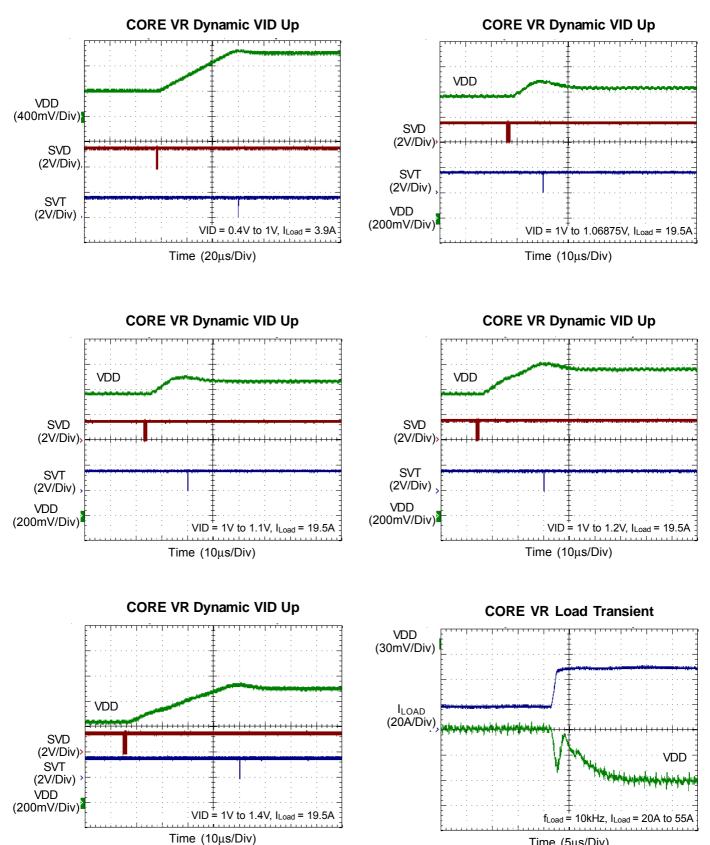

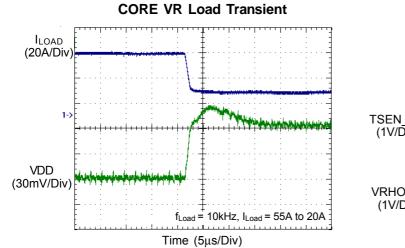

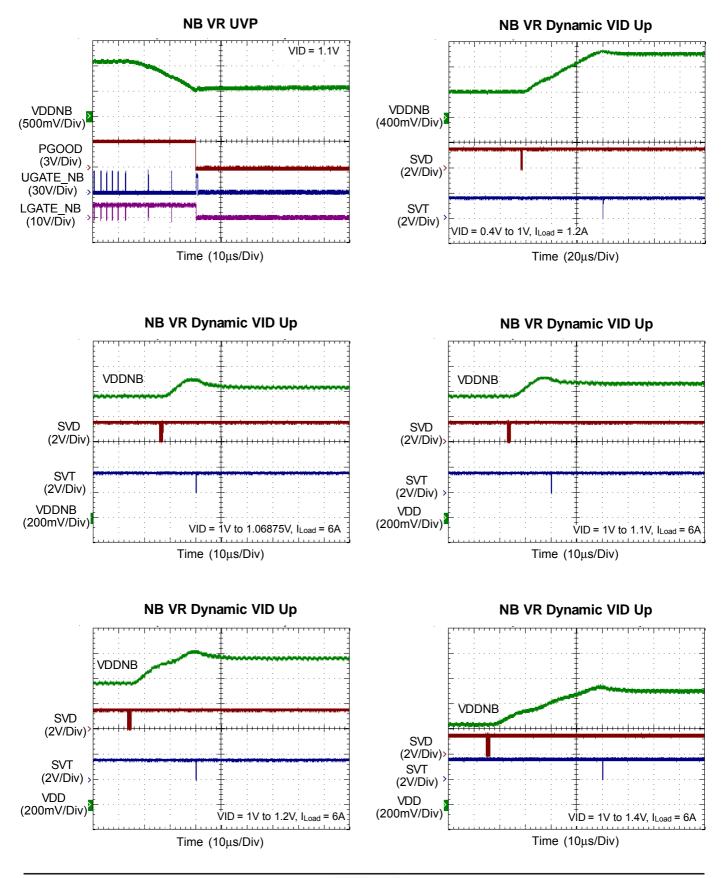

### **Typical Operating Characteristics**

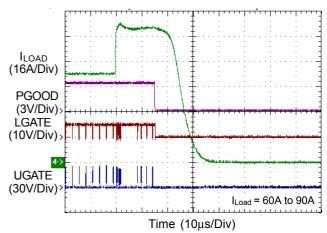

CORE VR OCP\_SPIKE

Copyright ©2019 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

Time (5µs/Div)

Copyright ©2019 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

Copyright ©2019 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

### **Application Information**

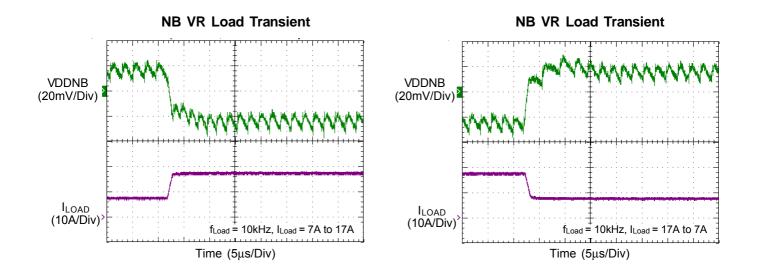

#### Power Ready (POR) Detection

During start-up, the RT3662AM will detect the voltage at the voltage input pins: VCC, PVCC and EN. When VCC > 4.3V and PVCC > 3.85V, the IC will recognize the power state of system to be ready (POR = high) and wait for enable command at the EN pin. After POR = high and V<sub>EN</sub> > 2V, the IC will enter start-up sequence for both VDD and VDDNB rail. If the voltage of VCC and EN pin drop below low threshold, the IC will enter power down sequence and all the functions will be disabled. Normally, connecting system power to the EN pin is recommended. The SVID will be ready in 2ms (max) after the chip has been enabled. All the protection latches (OVP, OCP, UVP) will be cleared only after POR = low. The condition of V<sub>EN</sub> = low will not clear these latches.

Figure 1. Power Ready (POR) Detection

#### Boot VID

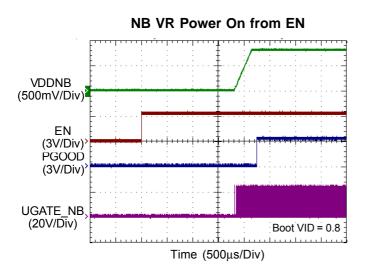

When EN goes high, both VDD and VDDNB output begin to soft-start to the Boot VID in CCM. Table 7 shows the Boot VID setting. The Boot VID is determined by the SVC and SVD input states at EN rising edge and it is in the internal register. The digital soft-start circuit ramps up the reference voltage at a controlled slew rate to reduce inrush current during start-up. When all the output voltages are above power good threshold (300mV below Boot VID) at the end of soft-start, the controller asserts power good (PGOOD) after a time delay.

|  | Table 7. 2-Bit Boot VID Code |  |

|--|------------------------------|--|

|--|------------------------------|--|

| Initial Startup VID (Boot VID)      |   |     |  |  |  |  |  |  |

|-------------------------------------|---|-----|--|--|--|--|--|--|

| SVC SVD VDD/VDDNB Output Voltage (V |   |     |  |  |  |  |  |  |

| 0                                   | 0 | 1.1 |  |  |  |  |  |  |

| 0                                   | 1 | 1.0 |  |  |  |  |  |  |

| 1                                   | 0 | 0.9 |  |  |  |  |  |  |

| 1                                   | 1 | 0.8 |  |  |  |  |  |  |

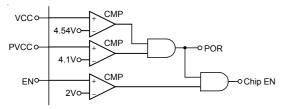

#### Start-Up Sequence

After EN goes high, the RT3662AM starts up and operates according to the initial settings. Figure 2 shows the simplified sequence timing diagram. The detailed operation is described in the following.

# RICHTEK

Description of Figure 2 :

T0: When the VIN power is ready, the RT3662AM will wait for VCC and PVCC POR.

T1: VDDIO power is ready, and the BOOT VID can be set by SVC pin and SVD pin, and latched at EN rising edge. SVT is driven high by the RT3662AM.

T2: The enable signal goes high and all output voltages ramp up to the Boot VID in CCM. The soft-start slew rate is 2.5mV/ms.

T3: All output voltages are within the regulation limits and the PGOOD signal goes high.

T4: The PWROK pin goes high and the SVI2 interface starts running. The RT3662AM waits for SVID command from processor.

T5: A valid SVID command transaction occurs between the processor and the RT3662AM.

T6: The RT3662AM starts VOTF (VID on-the-Fly) transition according to the received SVID command and send a VOTF Complete if the VID is greater than BOOT VID and reaches target VID.

T7: The PWROK pin goes low and the SVI2 interface stops running. All output voltages go back to the Boot VID in CCM.

T8: The PWROK pin goes high again and the SVI2 interface starts running. The RT3662AM waits for SVID command from processor.

T9: A valid SVID command transaction occurs between the processor and the RT3662AM.

T10: The action is same with T6. The RT3662AM starts VID on-the-Fly transition and send a VOTF Complete if the VID up and reaches target VID.

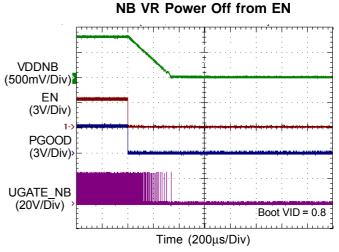

T11: The enable signal goes low and all output voltages enter soft-shutdown mode. The soft-shutdown slew rate is 2.5mV/ms.

#### **Power-Down Sequence**

If the voltage at the EN pin falls below the enable falling threshold, the controller is disabled. The voltage at the PGOOD pin will immediately go low when EN pin signal goes low, and the controller executes soft-shutdown operation. The internal digital circuit ramps down the reference voltage at the same slew rate as that of in softstart, making VDD and VDDNB output voltages gradually decrease in CCM. The Boot VID information stored in the internal register is cleared at POR. This event forces the RT3662AM to check the SVC and SVD inputs for a new boot VID when the EN voltage goes high again.

#### PGOOD

The PGOOD is open-drain logic output. It provides the power good signal when VDD and VDDNB output voltage are within the regulation limits and no protection is triggered. The pin is typically tied to 3.3V or 5V power source through a pull-high resistor. During shutdown state (EN = low) and the soft-start period, the PGOOD voltage is pulled low. After a successful soft-start and VDD and VDDNB output voltages are within the regulation limits, the PGOOD is released high.

The voltage at the PGOOD pin will be pulled low when any of the following events occurs : over-voltage protection, under-voltage protection, over-current protection, and logic low EN voltage. If one rail triggers protection, the PGOOD will be pull low.

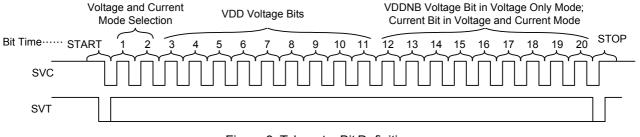

#### SVI2 Wire Protocol